### **International Journal of Electronics**

ISSN: 0020-7217 (Print) 1362-3060 (Online) Journal homepage: https://www.tandfonline.com/loi/tetn20

## Performance evaluation of an architecture for the characterisation of photo-devices: design, fabrication and test on a CMOS technology

G. Castillo-Cabrera , J. García-Lamont , M.A. Reyes-Barranca , J.A. Moreno-Cadenas & A. Escobosa-Echavarría

**To cite this article:** G. Castillo-Cabrera , J. García-Lamont , M.A. Reyes-Barranca , J.A. Moreno-Cadenas & A. Escobosa-Echavarría (2011) Performance evaluation of an architecture for the characterisation of photo-devices: design, fabrication and test on a CMOS technology, International Journal of Electronics, 98:3, 322-337, DOI: <a href="https://doi.org/10.1080/00207217.2010.538901">10.1080/00207217.2010.538901</a>

To link to this article: <a href="https://doi.org/10.1080/00207217.2010.538901">https://doi.org/10.1080/00207217.2010.538901</a>

|                | Published online: 10 Mar 2011.            |

|----------------|-------------------------------------------|

| Ø.             | Submit your article to this journal 🗷     |

| <u>lılıl</u>   | Article views: 90                         |

| Q <sup>L</sup> | View related articles 🗷                   |

| 4              | Citing articles: 1 View citing articles 🗗 |

# Performance evaluation of an architecture for the characterisation of photo-devices: design, fabrication and test on a CMOS technology

G. Castillo-Cabrera<sup>a</sup>\*, J. García-Lamont<sup>b</sup>, M.A. Reyes-Barranca<sup>c</sup>, J.A. Moreno-Cadenas<sup>c</sup> and A. Escobosa-Echavarría<sup>d</sup>

<sup>a</sup>Instituto Politécnico Nacional, ESCOM, Mexico City, Mexico; <sup>b</sup>UAEH-CITIS, Carretera Pachuca-Tulancingo km. 4.5, Pachuca, Mexico; <sup>c</sup>Centro de Investigación y de Estudios Avanzados del I.P.N., Electrical Engineering SEES, Av, Instituto Politecnico Nacional 2508, San Pedro Zacatenco, Mexico City, 07360 Mexico; <sup>d</sup>I.P.N. CINVESTAV, Electrical Engineering SEES, Av, Instituto Politecnico Nacional 2508, Mexico, City, Mexico

(Received 2 February 2010; final version received 10 August 2010)

In this report, the performance of a particular pixel's architecture is evaluated. It consists mainly of an optical sensor coupled to an amplifier. The circuit contains photoreceptors such as phototransistors and photodiodes. The circuit integrates two main blocks: (a) the pixel architecture, containing four p-channel transistors and a photoreceptor, and (b) a current source for biasing the signal conditioning amplifier. The generated photocurrent is integrated through the gate capacitance of the input p-channel MOS transistor, then converted to voltage and amplified. Both input transistor and current source are implemented as a voltage amplifier having variable gain (between 10dB and 32dB). Considering characterisation purposes, this last fact is relevant since it gives a degree of freedom to the measurement of different kinds of photo-devices and is not limited to either a single operating point of the circuit or one kind and size of photo-sensor. The gain of the amplifier can be adjusted with an external DC power supply that also sets the DC quiescent point of the circuit. Design of the row-select transistor's aspect ratio used in the matrix array is critical for the pixel's amplifier performance. Based on circuit design data such as capacitance magnitude, time and voltage integration, and amplifier gain, characterisation of all the architecture can be readily carried out and evaluated. For the specific technology used in this work, the spectral response of photo-sensors reveals performance differences between phototransistors and photodiodes. Good approximation between simulation and measurement was obtained.

**Keywords:** photo-transistors; photo-diodes; pixel architecture; spectral response; crosstalk

#### 1. Introduction

Image processing is a research field still in study for a wide variety of applications, such as picture and video digital cameras for entertainment use, pattern recognition based on artificial neural networks, real time object tracking and artificial vision for application in silicon retinas, among others. So, it is important to evaluate the performance of available integrated photo-sensor devices used in these applications,

<sup>\*</sup>Corresponding author. Email: gcastilloc@ipn.mx

considering issues as noise, resolution, processing time, colour, etc. Actually, there are several technologies available for integration of photo devices, commonly CCD, BiCMOS and GaAs. Although all of them are usually applied in image acquisition systems, there are still some performance aspects that should be optimised, such as voltage levels, leakage currents, high fabrication costs, etc., so research is still being done to overcome these limitations. Standard CMOS integrated circuit technology is also an attractive alternative, since devices like phototransistors and photodiodes can be implemented as well. It should be mentioned that this technology also has some limitations but since fabrication of CMOS integrated circuits has a low cost, exploration of the potential of new technologies for image processing is still an interesting field. Besides, algorithms can be implemented for tasks such as border detection (space vision), movement detection (space-time vision), image enhancement (image processing vision) and pattern classification or recognition (neuro-fuzzy vision).

In this work a chip was designed and fabricated with two possible photo-sensor structures: p+/N-well/p-substrate for photodiodes, through standard 1.5  $\mu$ m AMI technology. In the future, it is the intention to design a second chip that must include electronics for image processing with pulse frequency modulation (PFM), once the characterisation gives enough information about the performance of the stages studied.

#### 2. Architecture configuration

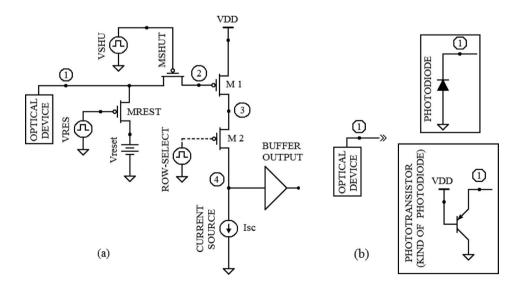

For image sensing tasks such as objects or scene capture, a matrix array of pixels is used. Figure 1 shows the architecture of a basic pixel cell used for the characterisation reported here. It consists either of a phototransistor or a photodiode that generates a photocurrent which is integrated at the gate of the p-channel transistor M1, loaded with a current source, Isc. M2 is mainly used for row selection in a matrix array and strictly speaking is not part of the amplifier that is used to

Figure 1. (a) Architecture of the pixel with the coupling amplifier. (b) Photo-devices.

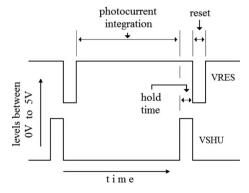

handle the photocurrent. Nevertheless, the position of M2 within the circuit plays a very important role, as will be established in section 3. Transistors MSHUT and MREST operate as switches in order to integrate the photocurrent generated in the photo-sensor at a given time and operation frequency. Figure 2 shows the waveforms of their respective gate voltages. Integration time,  $\Delta t$ , takes place while MSHU is on and MRES is off. During this time, the photocurrent is converted to voltage at the gate of transistor M1 (node 2 in Figure 1). The relation between the integrated voltage and photocurrent is expressed in Equation (1), assuming that the photocurrent is uniform in time. The block named OUTPUT BUFFER couples the input amplifier with the external measurement set-up. The DC voltage source, Vreset, is the reference voltage from which integration of the photocurrent is carried out.

$$I_{ph} = C_T(\Delta V_{\rm int}/\Delta T) \tag{1}$$

where  $I_{ph}$  is the photocurrent from the photo-device;  $C_T$  is the capacitance at node-2;  $\Delta V_{\rm int}$  is the integrated voltage in  $C_T$  ( $\Delta V_{in} = \Delta V_{\rm measured}/Av$ );  $\Delta T$  is the integration time; and Av is the amplifier's gain.

In addition, Vreset sets the quiescent point of the amplifier. Figure 2 shows the input voltage pulses applied to the gate of MRES and MSHUT.

As the objective of this work is to propose a methodology for the characterisation of photo-devices and pixel architectures, the design was made considering those parameters affecting the performance of pixels and the way they will be measured. The design was carried out carefully in order to use a simple architecture, as reported with current amplifiers in the current-mode readout configuration (Huang 2002, Lamont 2002). Rather, the amplifier is configured for voltage-mode operation in this case. From results obtained with this design, useful information can be processed and analysed considering a specific application, regarding factors such as the spectral response and silicon integration area of p+/N-well/p-substrate phototransistors and N-well/p-substrate photodiodes, as well as integration time, integrated voltage, transistors' aspect ratios and reference voltage used, for instance. Consideration about technology parameters is also important in defining the dependence of the response and the architecture operation upon the photo-device structure.

Figure 2. Waveform signals for shutter and reset transistors.

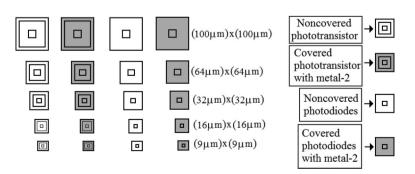

Here, we present the electronic design, layout, simulations and some measurements of the fabricated chip. This prototype was made using 1.5  $\mu$ m AMI technology. The chip contains five pairs of phototransistors and five pairs of photodiodes, with one instance of each pair covered with metal for dark current characterisation purposes. Results reported here are only from those devices having an area of (9  $\mu$ m) × (9  $\mu$ m). Bigger photo-devices were also measured, but as they saturated the amplifier, no useful results were obtained. Figure 3 shows the fabricated array.

#### 3. Design methodology

#### 3.1. Baseline

Next, some design criteria for the circuit are defined. Transistors MREST and MSHUT are used as switches, so their sizes can be drawn with the minimum dimension features allowed by the technology. Channel modulation effects must be avoided with M1; therefore its channel length should be at least five times the minimum dimension allowed. Besides, for proper operation of the amplifier, it is recommended to choose a stable current source for biasing; thus, a cascode configuration was selected and designed for sourcing 20  $\mu$ A. Finally, transistor M2 allows the adjustment of the voltage gain of the amplifier giving a useful degree of freedom for the characterisation of the architecture and different devices. One more degree of freedom consists of the variation of voltage gain, which allows it to adapt to different conditions for other kinds of devices.

#### 3.2. Circuit analysis

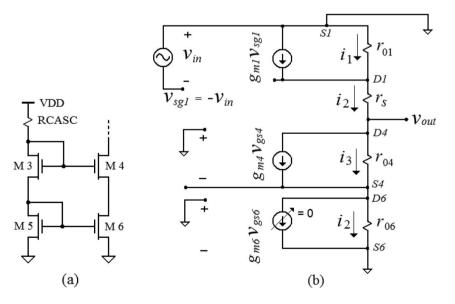

Figure 4(a) shows the schematic of the cascode current source used for biasing the amplifier. Transistors involved in the amplifier are M1, M2, M4 and M6. Figure 4(b) shows the equivalent circuit for the amplifier and the cascode current source, used to find a mathematical relationship between the voltage gain and the size of M2.

From Figure 4(b),  $r_s$  is the channel resistance of M2; here, subscripts 01, 04 and 06 are identifiers for transistors M1, M4 and M6, respectively. A circuit analysis gives the following expression for the output voltage,  $v_{out}$ :

$$r_{01}i_1 + r_si_2 + r_{04}i_3 + r_{06}i_2 = 0 (2)$$

Figure 3. Integrated phototransistors and photodiodes array.

$$i_2 - i_1 = g_{m1} v_{sg1} (3)$$

$$i_2 - i_3 = g_{m4} v_{gs4} \tag{4}$$

$$-v_{\text{out}} = r_{01}i_1 + r_si_2 \tag{5}$$

$$v_{\text{out}} = r_{04}i_3 + r_{06}i_2 \tag{6}$$

These are mesh equations from which the next expression is obtained:

$$R_0 i_2 = v_{\text{out}} \tag{7}$$

where:

$$R_0 = r_{04} + g_{m4}r_{06}r_{04} + r_{06} (8)$$

$$-i_1 + i_2 = g_{m1} v_{sg1} (9)$$

$$r_{01}i_1 + r_si_2 = -v_{\text{out}} \tag{10}$$

Using Equations (9) and (10),  $i_2$  can be obtained:

$$i_2 = \frac{r_{01}g_{m1}v_{sg1} - v_{out}}{r_s + r_{01}} \tag{11}$$

From Equations (7) and (11), the voltage gain of the amplifier is deduced:

$$R_0 \left( \frac{r_{01} g_{m1} v_{sg1} - v_{out}}{r_s + r_{01}} \right) = v_{out}$$

(12)

Figure 4. (a) Current source schematic circuit. (b) Equivalent circuit of the amplifier.

Defining the next ratio:

$$K = \frac{R_0}{r_s + r_{01}} \tag{13}$$

$$r_{01}g_{m1}v_{sg1}K - v_{out}K = v_{out}$$

(14)

and since

$$v_{sg1} = -v_{in} \tag{15}$$

$$Av = \frac{v_{\text{out}}}{v_{in}} \tag{16}$$

Finally the voltage gain is obtained:

$$Av = -\frac{K}{K+1}r_{01}g_{m1} \tag{17}$$

When  $K \gg 1$ , the gain can be approximated as:

$$Av \cong -r_{01}g_{m1} \tag{18}$$

This is only possible if  $r_s$  is sufficiently small, from Equation (13). So, assuming that  $r_{01} = r_{04} = r_{06}$  from Equations (8) and (13), the size of M2 must be such that  $r_s$  will result very small, compared with  $r_{01}$ ,  $r_{04}$  and  $r_{06}$ . With an iterative procedure, the aspect ratio W/L of M2 was made large enough such that  $r_s$  does not have a strong influence over the amplifier's operation (Baker, Li and Boyce 2005). So, for the technology used, the calculated aspect ratio for M2 was  $W = 64.8 \,\mu\text{m}$  and  $L = 2.4 \,\mu\text{m}$ . Then, considering these design outlines, the operation of the circuit based on M2 can be traduced in a convenient performance evaluation. As a result of the above design considerations, this basic analysis of the equivalent circuit reveals that the role of the row-select transistor is important for the proper operation of the amplifier. The voltage gain in Equation (18) can be estimated using the following expressions (Baker et al. 2005):

$$r_{01} = \frac{1}{\lambda I_D} \tag{19}$$

$$g_{m1} = \sqrt{2(KP)\frac{W}{L}I_D} \tag{20}$$

Using values of KP and  $\lambda$ , from the 1.5  $\mu$ m AMI technology, the maximum voltage gain was estimated to be Av = 35 dB.

#### 3.3. Simulation and Layout

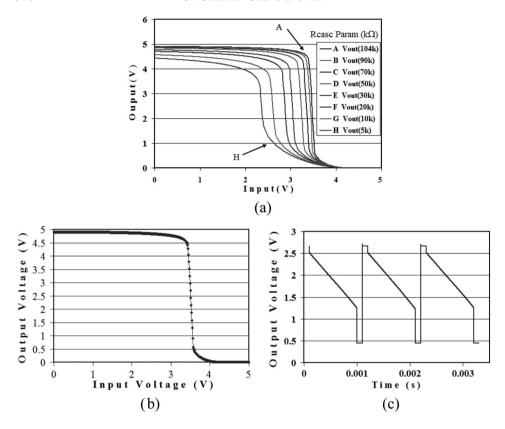

Once the sizes of transistors used in the pixel were calculated, simulations with PSPICE were made to confirm the behaviour of the circuit. Figure 5(a) shows the gain range that can be achieved with the amplifier, going from 10 dB to 32 dB. Figure 5(b) illustrates a transfer function with Av = 32 dB, used for the simulation presented in Figure 5(c), where the response of the photo-device can be seen,

Figure 5. PSPICE simulations (a) adjustable gain. (b) Transfer function of the voltage amplifier. (c) Output voltage response after excitation.

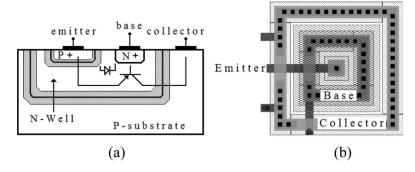

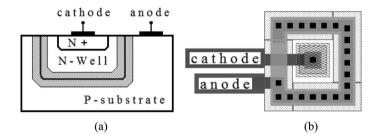

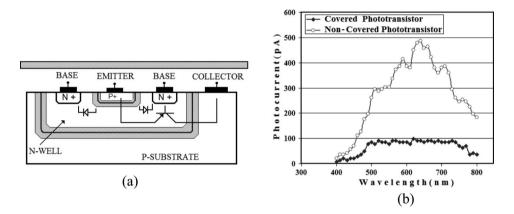

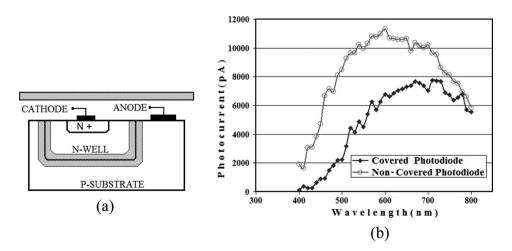

according with the waveforms of VSHU and VRES. It is also observed that  $V_{\rm reset}=3.5{\rm V}$ . The circuit was excited with a 10 pA current in order to simulate the photo response of the pixel. Levels of photocurrent excitation were obtained from Reginald-Krishna's model (Perry and Arora 1996). Figures 6 and 7 show the cross sections and layout of phototransistors and photodiodes designed for this chip. From Figure 6(a), it can be seen that the two p-n junctions are present in the phototransistor, i.e. p+/N-well and N-well/p-substrate. Obviously, p-n junctions should be reverse biased to operate correctly. The base-collector junction was biased with 5V and the base-emitter junction with  $(5{\rm V}-3.5{\rm V})=1.5{\rm V}$ . The photodiode junction is formed with the N-well/p-substrate layers. The ring above the base area of the phototransistor has the same dimensions of the photodiode's anode ring (9  $\mu$ m  $\times$  9  $\mu$ m). The photocurrent generated is collected by the phototransistor's emitter and the same happens with the cathode of the photodiode.

#### 4. Results

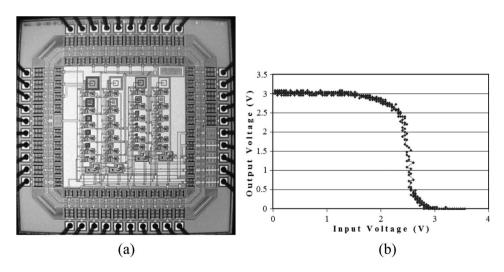

Figures 8(a) and (b) show a microphotograph of the fabricated chip and the measured transfer function of the amplifier, respectively. This transfer function can be practically adjusted from 10 dB to 32 dB by externally adjusting RCASC and Vreset (see Figures 1 and 4). Figures 9(a) and (b) show the voltage mode response of

Figure 6. Phototransistor: (a) cross section; (b) layout.

Figure 7. Photodiode: (a) cross section; (b) layout.

Figure 8. (a) Microphotograph of the fabricated chip; (b) measured transfer function of the amplifier.

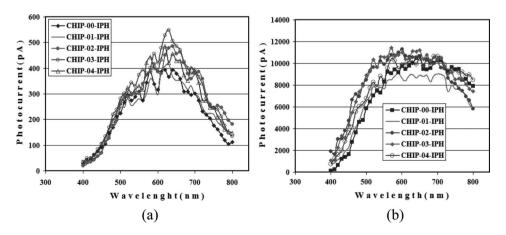

phototransistors and photodiodes, respectively. The measured voltage is used to estimate the integrated voltage at node 2 (see Figure 1). Also, Figures 9(a) and (b) show the dependence of the slope of integrated voltage to different optical power

applied to phototransistors and photodiodes, for a light wavelength of 470 nm. This wavelength was chosen since a better response was obtained, compared to the other wavelengths explored. The integration time in the case of the photodiodes (N-well/p-subs junction) is 0.5 ms, while in the case of phototransistors, made with p+N-well/p-subs junctions, it is 1.0 ms (see Figure 9).

The amplifier gain was set at 10 dB in the case of the photodiode measurements, and 32 dB for the phototransistors. The conditions were set in this way in order to have a good read (non-saturated photodiodes). It is clear that response of the photodiodes, shown in Figure 9(b), tends to be much larger than that of the phototransistors. This is an indication that the integrated current within the photodiode is higher compared to that of the phototransistor, even with the same incident illumination power. This is confirmed with the plots shown in Figure 10, where the photocurrent was estimated as a function of wavelength. The difference between them is about one order of magnitude. These responses were carefully obtained adjusting the gain of the amplifier and with experimental data of sensitive surface, capacitance in the node 2 and integration time. The photocurrent was estimated using Equation (1) and

Figure 9. (a) Voltage response of phototransistors (p+|N-well|p-subs). (b) Voltage response of photodiodes (N-well|p-subs).

Figure 10. (a) Spectral response of phototransistors (p+|N-well|p-subs). (b) Spectral response of photodiodes (N-well|p-subs). Five chips measured.

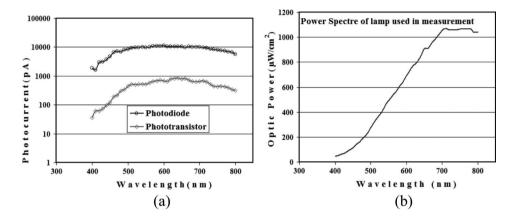

similar data from Figure 9. Here the technology spread can also be seen, as five chips were measured giving some dispersion from each photo-device measured. The resulting display logarithmic is shown in Figure 11(a). A HILGER & WATTS monochromator and an ISA lamp were used. The spectral characteristics of that lamp are shown in Figure 11(b).

For both  $(9 \mu m) \times (9 \mu m)$  phototransistors and photodiodes, the spectral response was measured. Figure 11(a) presents a comparison in magnitude between the spectral responses of phototransistors and photodiodes.

A kind of small oscillation can be observed from Figure 10. It is believed that this oscillation is due to Fabry-Perot interference (Bollschweiler et al. 2009, Liang et al. 2001).

Again, it can be seen that the photocurrent from the photodiode is higher than the photocurrent from the photocurrent from the phototransistor.

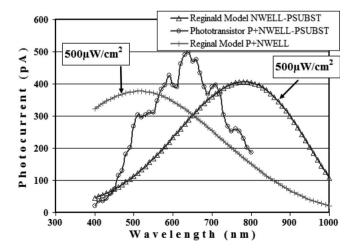

Figure 12 shows a comparison among the spectral response of the phototransistor used in this work (with 500  $\mu$ W/cm<sup>2</sup> optical power) and the reported

Figure 11. (a) Spectral response of p+/N-well/p-subs and N-well/p-subs structures; (b) power spectrum of the ISA lamp.

Figure 12. Reginald's models and measured spectral response (p+|N-well|p-subs).

Reginald-Krishna's model (Perry and Arora 1996) using two other similar photodiode structures. It should be noted that the experimental photo-response of the phototransistor has its maximum just where the junctions of N-well/p-subs and p+/N-well models overlap. The models plot the ideal photoresponse of the indicated junctions but they do not include parasitic currents generated by additional events such as crosstalk, for instance.

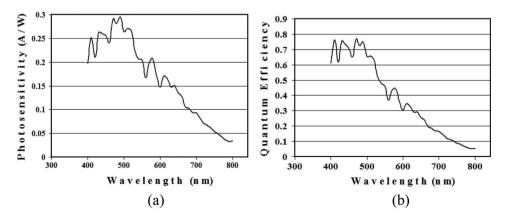

Crosstalk is a problem that can be present with neighbouring illuminated pixels that collect reflected or refracted light through lateral paths. Ideally, this should be avoided to minimise the degradation of pixels. Crosstalk can increase if the integration density of pixel arrays increases as technology shrinks the size of devices. Then, the experimental curve is shifted towards the right from the ideal p+/N-well curve. It should be remembered that the emitter-base junction is the active one in the phototransistor. Figure 13(a) and (b) show photosensitivity and quantum efficiency, respectively, for the measured phototransistors. The experimental photocurrent density was evaluated with Equation (21).

$$J_{ph} = \frac{C_T \cdot \Delta V_{in}}{A_{ph} \cdot \Delta T} \tag{21}$$

Where  $J_{ph}$  is the photo-sensor current density;  $C_T$  is the capacitance at node-2;  $\Delta V_{in}$  is the integrated voltage at node-2;  $A_{Ph}$  is the sensitive area of the phototransistor; and  $\Delta T$  is the integration time according to Figure 2.

The photosensitivity was evaluated using the following expression:

$$S_{\lambda} = \frac{J_{ph}}{P_{\text{opt}}} \tag{22}$$

Where  $P_{\text{opt}}$  is the optical power density from Figure 11(b).

The quantum efficiency QE was evaluated with:

$$QE = S_{\lambda} \frac{h \cdot c}{\lambda \cdot a} = 1240 \frac{S_{\lambda}}{\lambda} \tag{23}$$

Where  $hc/\lambda$  is the energy of photons, with  $\lambda$  in  $\mu$ m, and q is the charge of electrons.

Figure 13. p+/N-well/p-subs structure: (a) photosensitivity; (b) quantum efficiency.

#### 4. Discussion

The graphs shown in Figure 9 were made using a fixed wavelength with optical power as a parameter. After several measurements over the photo-devices 470 nm was selected since this wavelength gave the maximum sensitivity, as can be seen from Figure 13. With the structures used as photo-devices, a strong difference between the spectral photo-response of phototransistors and photodiodes can be identified. It can be seen from Figure 11(a) that for the same illumination conditions the response of photodiodes is higher than the response of phototransistors, by almost an order of magnitude. In addition, measurements were also made over structures covered with metal, and the results are shown in Figures 14 and 15 for phototransistors and photodiodes, respectively. In the case

Figure 14. p+/N-well/p-subs structure: (a) cross section covered with metal; (b) spectral response of covered and non-covered phototransistors.

Figure 15. N-well/p-subs structure: (a) cross section covered with metal; (b) spectral response of covered and non-covered photodiodes.

of phototransistors, it is seen that the response of covered devices is almost 85% weaker than that of a non-covered device.

In the case of photodiodes, this difference is lower – about 30% – and we believe that there is a big substrate leakage current due to the properties of the *N-well/p-subs* structure that may have other contributions adding to carriers directly generated by photons from inside the photodiodes' area. However, all of the measured current is stimulated by photons as we can see from Figure 15(b). Furthermore, it can be suggested that the *N-well/p-subs* structure used as a photodiode is not too efficient due to crosstalk, degrading pixel characteristics as the dynamic range, and increasing the fixed pattern noise.

It is reported that crosstalk is a mechanism that is pronounced at longer wavelengths (Lee et al. 2008) since light with these characteristics can go deep into silicon, with a high probability of being reflected by the different layers present in the structure of the pixel. This can be confirmed with Figure 15(b), where it is seen that the photocurrent of a covered photodiode increases as wavelength is increased. Furthermore, comparing Figures 14(b) and 15(b), it can be concluded that the base-collector junction of the phototransistor operates as a barrier for carriers generated by light that penetrates beyond the surface region into the substrate. Since the photodiode does not have this additional junction, it is collecting extra carriers, thus inconveniently reducing the difference between the response of covered and uncovered devices. This should also be considered when designing pixel architectures, providing the pixel with surrounding materials with low dielectric constants and index of refraction, as long as the technology allows it. Otherwise, junction barriers as base-collector in phototransistors can play a similar role. Due to the importance of this mechanism over the performance of pixels, the following explanation is given regarding crosstalk.

#### 4.1. Lateral crosstalk mechanism

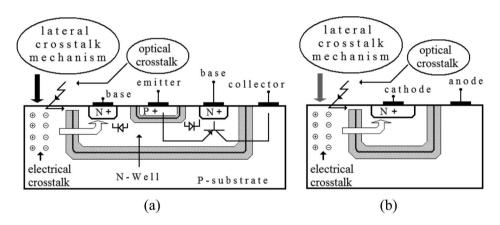

We have focused on the characterisation and analysis of the likely mechanisms that could contribute to the crosstalk in p+/N-Well/p-substrate (phototransistor) and N-Well/p-substrate (photodiode) structures. Of these kinds of photo-devices, crosstalk has been defined and classified into two main mechanisms: (a) optical crosstalk and (b) electrical crosstalk (Brouk et al. 2002, Kang 2002, Tabet 2002). Here we introduce an additional classification of crosstalk, as is shown in Figure 16. The first classification is lateral crosstalk mechanism which includes optical crosstalk (OC) and lateral electrical crosstalk (LEC).

Optical crosstalk is due to light travelling laterally among the layers up to the junction (near the surface of the device) acting as a waveguide, as is shown in Figure 16. LEC is the phenomenon whereby photons generate carriers 'near to the surface region'. That phenomenon has its origin in short wavelength light, mainly under 650 nm. Both optical and LEC crosstalk are present either in phototransistors or photodiodes. However, in phototransistors this contribution is as a photocurrent collected by the base contact, which is tied to VDD, hence masking the effect. This is the first reason why the photo-current is larger in photodiodes than in phototransistors. Figure 16(a) shows the way in which both OP and LEC mechanisms affect the response of phototransistors and Figure 16(b) shows the

corresponding for photodiodes. The effect is very strong since the current comes from all directions.

#### 4.2. Vertical crosstalk mechanism

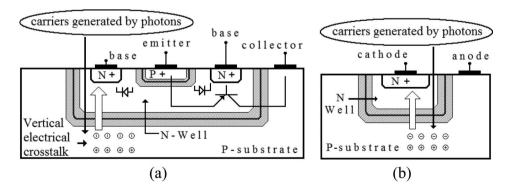

The vertical crosstalk mechanism is shown in Figure 17. It originates only due to electrical crosstalk, so it is called vertical electrical crosstalk (VEC). In the case of phototransistors, carriers generated along the substrate, as well as behind and outside the *N-Well*, are collected by the base contact since it is connected to a higher voltage than the emitter (see Figure 17(a)). So, only majority carriers are collected by the base.

In this case, diffusion of minority carriers is present as leakage current. Hence, little or no contribution to the spectral response of phototransistors is due to vertical electrical crosstalk. The vertical electrical crosstalk effect in photodiodes is illustrated in Figure 17(b).

Figure 16. Lateral crosstalk mechanism (a) in the phototransistor; (b) in photodiodes.

Figure 17. Vertical electrical crosstalk mechanism (a) in phototransistors; (b) in photodiodes.

Carriers generated by photons behind and outside the *N-Well* contribute to the spectral response of the photodiode with the leakage current coming from the substrate.

Carriers generated deep in the substrate are due to longer wavelengths. This component of leakage current has a very strong effect over photodiodes but this is not the case for phototransistors, so the difference appreciated in Figure 11 can be attributed to this.

#### 5. Conclusions

An architecture was proposed for the characterisation of photo-devices, giving useful information for the performance evaluation of junction structures available in CMOS standard technologies. An adjustable gain amplifier, with a gain range of 10 dB - 32 dB, was configured allowing different biasing and operating points for photo-response measurement of different devices. Good agreement between simulated and experimental transfer function of the amplifier was obtained. The row-select transistor, M2, plays an important role in the operation of the amplifier. It was found that the aspect ratio of this transistor should be high in order to have a small channel resistance and to ensure an adjustable gain property to the amplifier. On the other hand, phototransistors (p+|N-well|p-subs) and photodiodes (N-well/p-subs) were characterised for a 1.5 µm technology, but the same methodology can be used with other silicon foundries. Structures have a maximum quantum efficiency of about 0.7 and a maximum sensitivity of almost 0.3 A/W. Besides, photodiodes made with an N-well/P-subs junction have shown a strong substrate leakage current contribution due to crosstalk that can affect parameters such as dynamic range and fixed pattern noise. So, depending on the features added to the architecture and the technology available, photodiodes may not be a good choice for image sensor arrays.

#### References

- Baker, R.J., Li, H.W., and Boyce, D.E. (2005), CMOS, Circuit Design, Layout, and Simulation, New York: IEEE PRESS.

- Bollschweiler, L., English, A., Jacob Baker, R., Kuang, W., Chang, Z-C., Shih, M.H., Knowlton, W.B., Hughes, W.L., Lee, J., Yurke, B., Cockerham, N.S., and Tyree, V.C. (2009), 'Chip-scale nanophotonic chemical and biological sensors using CMOS process'. Proceedings of the 52nd IEEE International Midwest Symposium on Circuits and Systems, 2009. MWSCAS '09. Aug. 2–5, 2009, Cancún, Mexico, pp. 913–916.

- Brouk, I., Nemirovsky, Y., Lachowicz, S., Gluszak, E.A., Hinckley, S., and Eshraghian, K. (2002), 'Characterization of crosstalk between CMOS photodiodes', *Solid-State Electronics*, 46, 53–59.

- Huang, Y. (2002), Current-Mode CMOS Image sensor, Master in Applied Science in Electrical Engineering Thesis, presented to the University of Waterloo, Electrical Engineering Department; Ontario, Canada.

- Kang, I.M. (2002), 'The simulation of the crosstalk between Photodiodes Fabricated Using the 0.18μm CMOS Process', in *SMDL Annual Report 2002*, School of Electrical Engineering, Seoul National University.

- Lamont, J.G. (2002), 'Optical Sensor CMOS Prototype with Parallel Processing', unpublished Ph.D. thesis, CINVESTAV-Mexico: Department of Electrical Engineering.

- Lee, Ji, Mouli, and Chandra, (2008), United States Pntent 7315014.

- Liang, W., Bockrath, M., Bozovic, D., Hafner, J.H., Tinkham, M., and Park, H. (2001), 'Fabry-Perot interference in a nanotube electron waveguide', *Journal of Nature*, 411(7), 665–669.

- Perry, R.J., and Arora, K. (1996), 'Using PSPICE to simulate the photoresponse of ideal CMOS Integrated Circuits Photodiodes', *Proceedings of the IEEE Southeastcon Bringing Together Education, Science and Technology*, pp. 374–380.

- Tabet, M. (2002), 'Double Sampling Techniques for CMOS Image Sensors', PhD thesis, University of Waterloo Electrical and Computer Engineering. Waterloo, Ontario, Canada.