## CENTRO DE INVESTIGACIÓN Y DE ESTUDIOS AVANZADOS DEL INSTITUTO POLITÉCNICO NACIONAL

# UNIDAD ZACATENCO DEPARTAMENTO DE INGENIERÍA ELÉCTRICA SECCIÓN DE ELECTRÓNICA DEL ESTADO SÓLIDO

## Diseño de un interruptor de RF-MEMS como alternativa para el funcionamiento cuasi-flotante del FGMOS

Tesis que presenta:

ING. BENITO GRANADOS ROJAS

Para obtener el grado de:

**MAESTRO EN CIENCIAS**

EN LA ESPECIALIDAD DE INGENIERÍA ELÉCTRICA

Director de Tesis:

DR. MARIO ALFREDO REYES BARRANCA

México, D.F. Agosto, 2015

#### Agradecimientos

Agradezco a todos aquellos que me impulsaron para alcanzar esta nueva meta.

Y con mucho cariño dedico este trabajo a mi familia, por ser la fuente de inspiración y el soporte de todos los nuevos proyectos que emprendo. Cada uno de los pasos que doy obtiene su fuerza de ellos.

Extiendo también mi más grande agradecimiento a mi asesor, el Dr. Alfredo Reyes Barranca, por la gran confianza que depositó sobre mí desde el primer momento y el entusiasmo que me contagió para desarrollar una más de mis metas académicas.

Siendo invaluable su ayuda, agradezco de igual manera al M. en C. Luis Martín Flores Nava por respaldar mis ideas y estar siempre en la mejor disposición de analizar, debatir y solucionar las inquietudes académicas del día a día.

En cuanto a la mejora y correcciones del presente trabajo, agradezco a los profesores sinodales, Dr. José Antonio Moreno Cadenas y Dr. Felipe Gómez Castañeda, por su tiempo y por la completa y oportuna revisión.

No menos importante, comparto también la satisfacción de este nuevo logro con todos mis compañeros estudiantes del grupo de Sistemas VLSI, con los que compartí valiosos momentos de trabajo y diversión.

Incluyo por último, mi agradecimiento al personal académico y administrativo de la Sección de Electrónica del Estado Sólido y al **CONACyT** por todos los recursos y apoyo otorgados para la realización de este trabajo.

A todos, gracias.

Benito Granados Rojas

Agosto, 2015

### Contenido

| C  | ontenio  | loI                                 |

|----|----------|-------------------------------------|

| ĺr | ndice de | e figurasIII                        |

| ĺr | ndice de | e tablasV                           |

| R  | esumei   | າVI                                 |

| Α  | bstract  | ·VII                                |

| 0  | bjetivo  | sVIII                               |

| Jι | ıstifica | ciónIX                              |

| 1. | Intr     | oducción1                           |

|    | 1.1.     | Antecedentes                        |

|    | 1.1.1.   | MEMS y su clasificación             |

|    | 1.1.2.   | Tecnología CMOS estándar            |

|    | 1.1.3.   | Compuerta flotante                  |

|    | 1.1.4.   | Micromaquinado                      |

|    | 1.2.     | Aplicaciones y estado del arte21    |

|    | 1.3.     | MEMS electrostáticos                |

|    | 1.4.     | Reglas de escalamiento              |

|    | 1.5.     | Elementos capacitivos               |

|    | 1.5.1.   | Estructuras capacitivas básicas     |

|    | 1.5.2.   | Sistema masa-resorte                |

|    | 1.5.3.   | Simulación multifísica              |

|    | 1.6.     | Conclusiones del capítulo           |

| 2. | Asp      | ectos teóricos35                    |

|    | 2.1.     | Actuación electrostática35          |

|    | 2.1.1.   | Capacitancia entre placas paralelas |

|    | 2.1.2.   | Capacitancia lateral                |

|    |          | Fuerza Electrostática               |

|    | 2.1.4.   | Punto de Equilibrio43               |

|    | 2.2.    | El efecto Joule                                | 46   |

|----|---------|------------------------------------------------|------|

|    | 2.3.    | Desempeño como interruptor                     | 51   |

|    | 2.3.1.  | Pérdidas de inserción                          | 52   |

|    | 2.3.2.  | Aislamiento                                    | 53   |

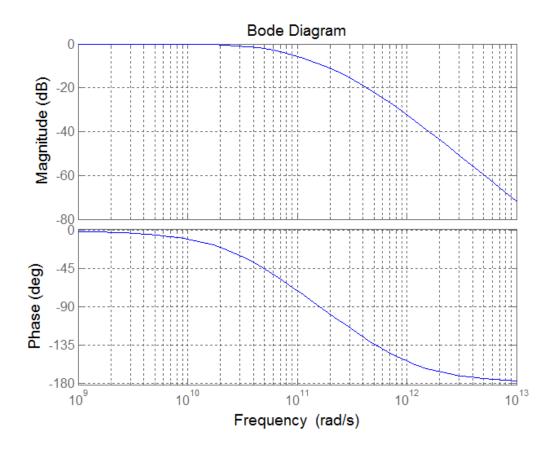

|    | 2.3.3.  | Respuesta en frecuencia                        | 54   |

|    | 2.4.    | El transistor MOS de compuerta flotante        | 57   |

|    | 2.5.    | Conclusiones del capítulo                      | 64   |

| 3. | Mét     | odos de diseño                                 | 67   |

|    | 3.1.    | Geometría y diseño topológico                  | 68   |

|    | 3.2.    | Elementos microelectromecánicos                | 69   |

|    | 3.3.    | Compuerta flotante en tecnología CMOS          | 72   |

|    | 3.4.    | Elementos auxiliares                           | .74  |

|    | 3.5.    | Modelo multifísico                             | 76   |

|    | 3.6.    | Conclusiones del capítulo                      | . 77 |

| 4. | Mét     | odos de prueba                                 | 79   |

|    | 4.1.    | Simulación electromecánica por elemento finito | . 79 |

|    | 4.2.    | Simulación eléctrica en plataforma SPICE       | 87   |

|    | Conclu  | siones del capítulo                            | 92   |

| 5. | Con     | clusiones generales                            | 93   |

|    | 5.1.    | Aportaciones                                   | . 94 |

|    | 5.2.    | Trabajo futuro                                 | . 95 |

| Re | eferenc | ias bibliográficas                             | 96   |

| 4r | пехо А  |                                                | 98   |

| 4r | пехо В  |                                                | 01   |

|    |         |                                                |      |

|    | _       |                                                |      |

## Índice de figuras

| Figura 1-1. Acelerómetro MEMS de uso principalmente académico Sparktun ADXL345                   | 1       |

|--------------------------------------------------------------------------------------------------|---------|

| Figura 1-2. Elementos de un sistema microsensor básico                                           | 2       |

| Figura 1-3. Elementos de un sistema microactuador básico                                         | 2       |

| Figura 1-4. Microfotografía SEM de un microactuador (manipulador robótico)                       | 3       |

| Figura 1-5. John Bardeen, William Shockley y Walter Brattain en los laboratorios Bell, 1948      | 4       |

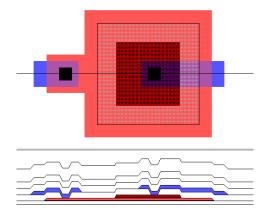

| Figura 1-6. Diagrama de transistores NMOS y PMOS en la tecnología CMOS estándar                  | 9       |

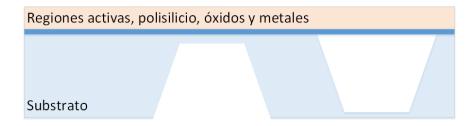

| Figura 1-7. Primera capa de polisilicio en el proceso CMOS estándar                              | 12      |

| Figura 1-8. Esquema de capas de materiales en el proceso OnSemi C5N de 0.5μm                     | 13      |

| Figura 1-9. Configuración de compuerta en transistor (a) MOS convencional (b) FGMOS              | 15      |

| Figura 1-10. Desplazamiento del voltaje de umbral en el FGMOS                                    | 15      |

| Figura 1-11.Inyección por electrones calientes.                                                  | 16      |

| Figura 1-12. Inyección de carga por tunelamiento Fowler-Nordheim                                 |         |

| Figura 1-13. Inyección Fowler-Nordheim autolimitada                                              | 17      |

| Figura 1-14. Inyección de carga mediante un interruptor electromecánico                          | 17      |

| Figura 1-15. Esquema de cavidades en el micromaquinado volumétrico                               | 21      |

| Figura 1-16. Esquema del micromaquinado superficial                                              |         |

| Figura 1-17. Reportes de la literatura en RF-MEMS                                                |         |

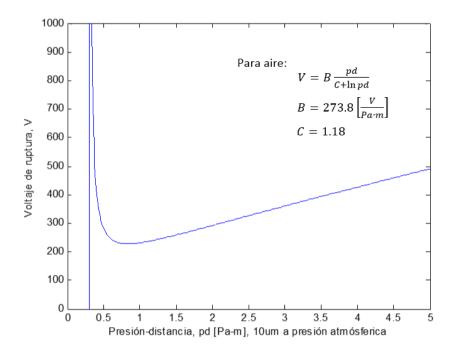

| Figura 1-18. Curva de Paschen para el aire a presión atmosférica: el factor pd [Pa-m] represe    | enta en |

| el eje horizontal múltiplos de una separación d (10μm) a una presión p (aire a presión           |         |

| atmosférica)                                                                                     | 27      |

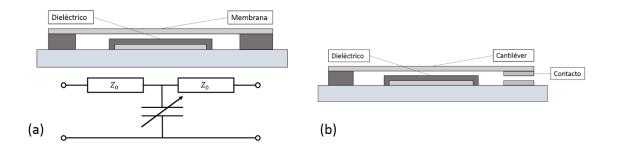

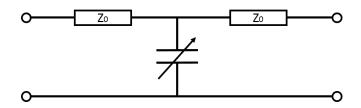

| Figura 1-19. Interruptores electrostáticos (a) tipo shunt y circuito eléctrico equivalente, donc | de      |

| Z0 es la impedancia de la línea de transmisión, (b) tipo óhmico en configuración cantiléver.     | 29      |

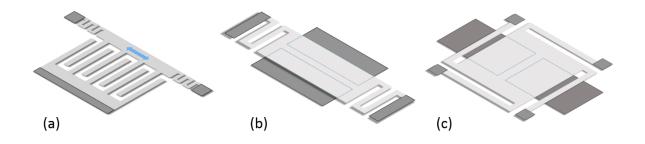

| Figura 1-20. Transductores capacitivos (a) tipo peine [comb-drive], (b) membrana rectangula      | ar con  |

| dos resortes, (c) membrana cuadrada con cuatro resortes                                          |         |

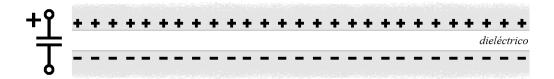

| Figura 1-21. Símbolo y distribución de cargas en un capacitor de placas paralelas                |         |

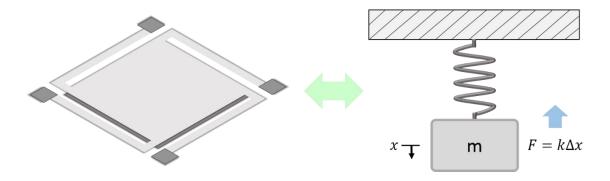

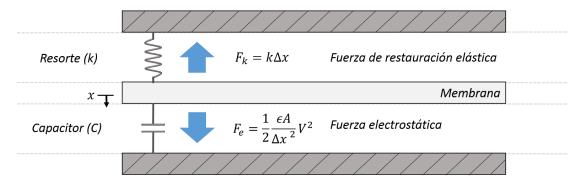

| Figura 1-22. Estructura capacitiva suspendida y sistema mecánico equivalente                     |         |

| Figura 1-23. Equilibrio entre las fuerzas elástica y electrostática                              |         |

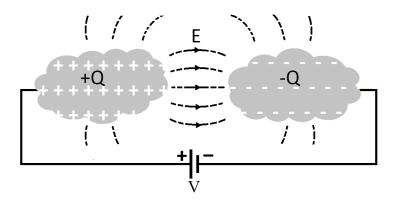

| Figura 2-1. Capacitor de dos conductores                                                         |         |

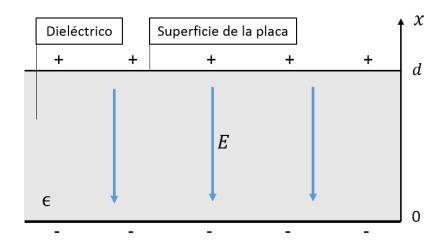

| Figura 2-2. Capacitor de placas paralelas                                                        |         |

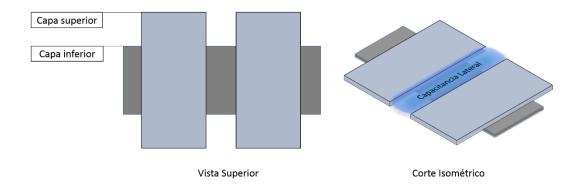

| Figura 2-3. Esquema de capacitancia lateral en elementos coplanares                              | 40      |

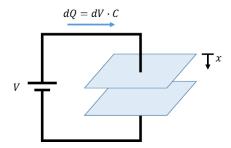

| Figura 2-4. Esquema de un capacitor C conectado a una fuente de voltaje V                        |         |

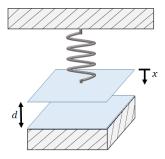

| Figura 2-5. Esquema de un transductor de placas paralelas enlazado a un resorte k                |         |

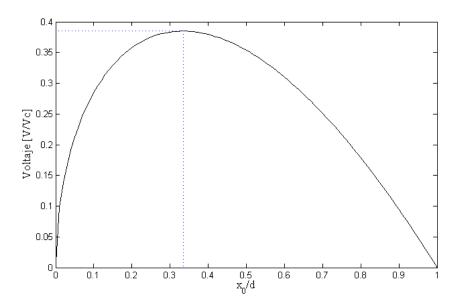

| Figura 2-6 Punto de inflexión en voltaje vs. desplazamiento                                      |         |

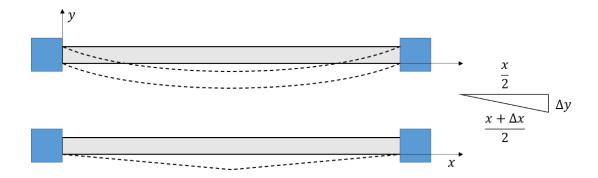

| Figura 2-7. Flexión por elongación en viga doblemente empotrada                                  |         |

| Figura 2-8. Efectos de la elongación de los resortes de suspensión                               |         |

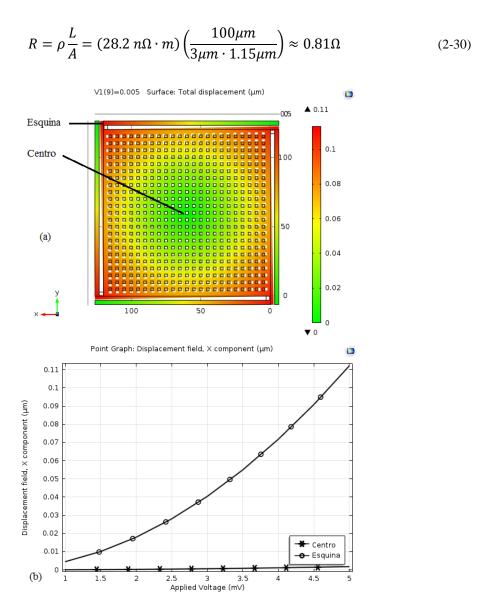

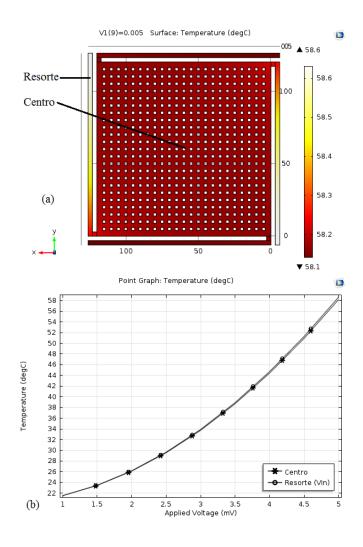

| Figura 2-9. Deformación de la membrana de aluminio sometida a calentamiento Joule                | 49      |

| Figura 2-10. Distribución e incremento de la temperatura por calentamiento Joule                 |         |

| Figura 2-11. Esquema de línea de transmisión típica en los sistemas RF-MEMS                      |         |

| Figura 2-12. Circuito equivalente de línea de transmisión con carga                              | 52      |

| Diseño de un interruptor de RF-MEMS como alternativa para el funcionamiento cuasi-flotante del F | GMOS    |

| Figura 2-13. Circuito equivalente en c.d. del interruptor en modo de conducción (on)                | 53   |

|-----------------------------------------------------------------------------------------------------|------|

| Figura 2-14. Circuito equivalente en c.d. del interruptor en modo de corte (off)                    | 53   |

| Figura 2-15. Circuito de impedancias equivalentes para análisis en frecuencia                       | 54   |

| Figura 2-16. Diagrama de Bode del circuito equivalente                                              | 56   |

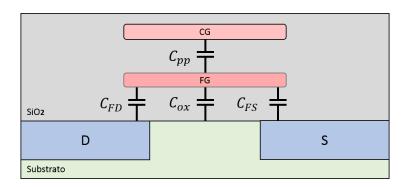

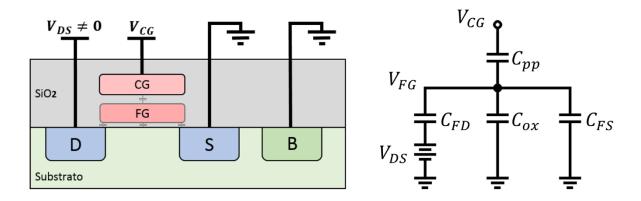

| Figura 2-17. Estructura y capacitancias del transistor FGMOS.                                       | 57   |

| Figura 2-18. Estructura principal (simplificada) del FGMOS y circuito equivalente                   | 58   |

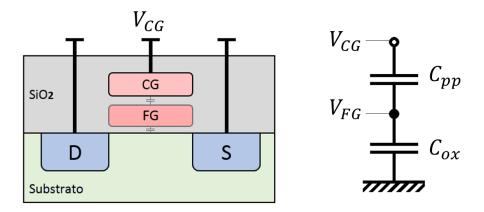

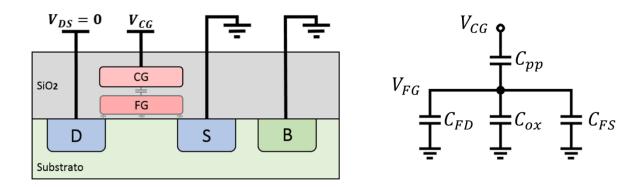

| Figura 2-19. Estructura capacitiva del FGMOS en $\mathit{VDS} = \mathit{0V}$ y circuito equivalente | 60   |

| Figura 2-20. Estructura capacitiva del FGMOS en $VDS \neq 0V$ y circuito equivalente                | 61   |

| Figura 2-21. Análisis de nodos y mallas en el arreglo de impedancias del transistor FGMOS           | 62   |

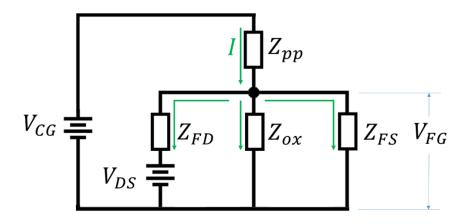

| Figura 3-1. Proceso de diseño.                                                                      |      |

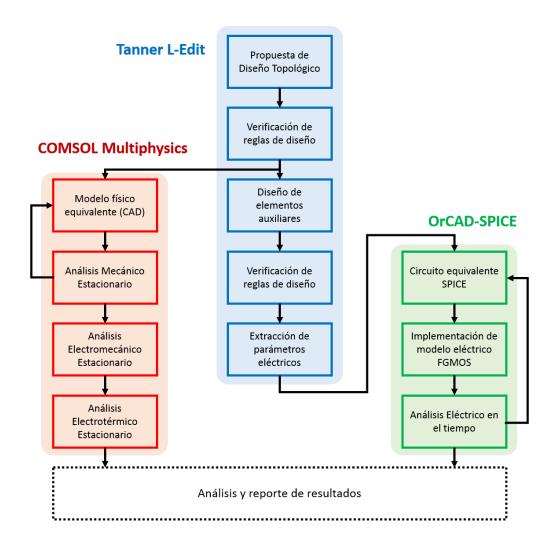

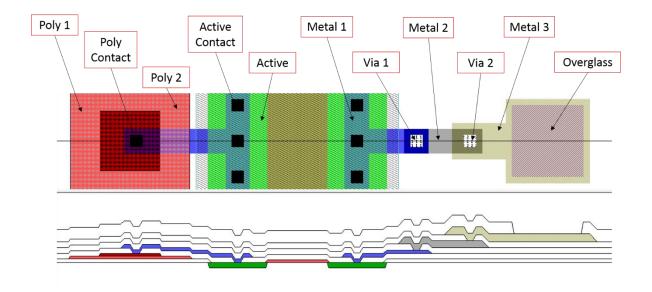

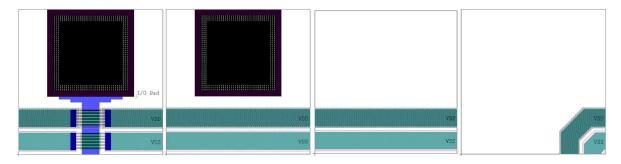

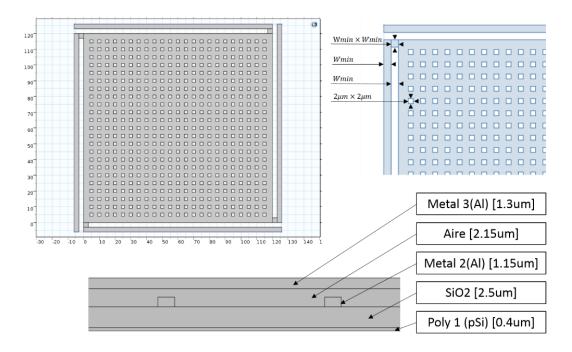

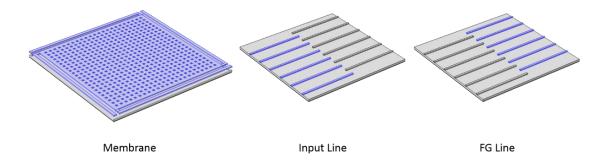

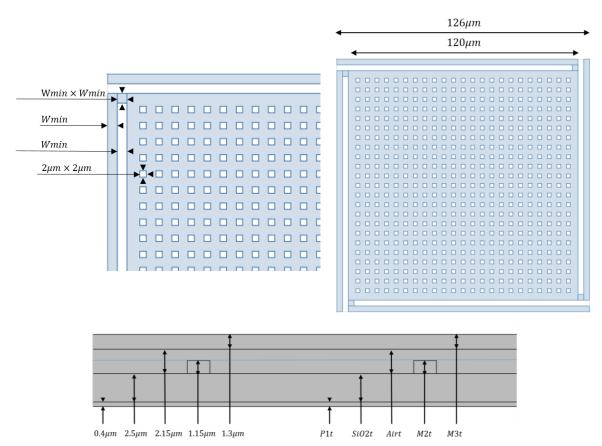

| Figura 3-2. Capas y corte transversal de la tecnología AMIS 0.5                                     |      |

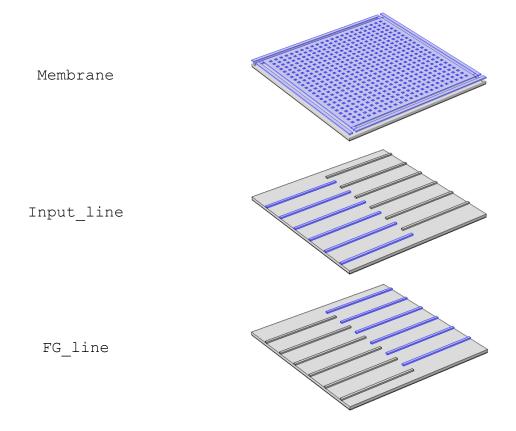

| Figura 3-3. Estructura tipo membrana propuesta.                                                     |      |

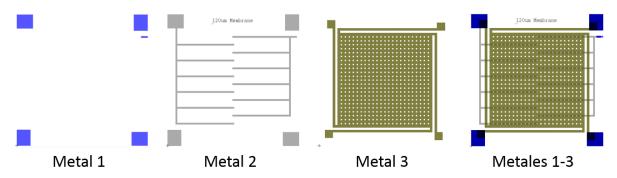

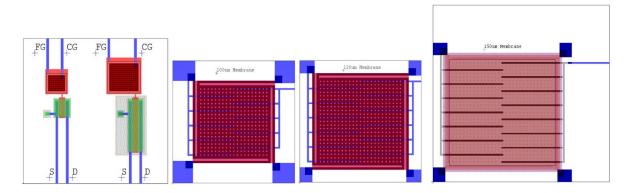

| Figura 3-4. Secuencia de metales 1 a 3 en la estructura de membrana                                 | 70   |

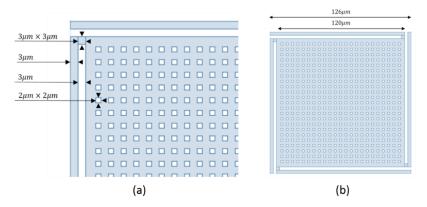

| Figura 3-5. Dimensiones propuestas para la membrana base de $120 \mu m$                             | 70   |

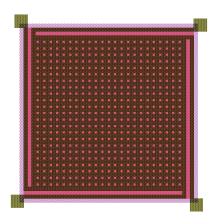

| Figura 3-6. Superposición de Poly 1 y Metal 3 en la estructura de membrana                          |      |

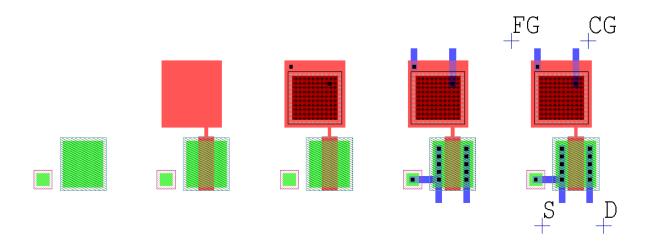

| Figura 3-7. Capacitor Poly 1 – Poly 2                                                               | 73   |

| Figura 3-8. Transistores NMOS y PMOS convencionales.                                                |      |

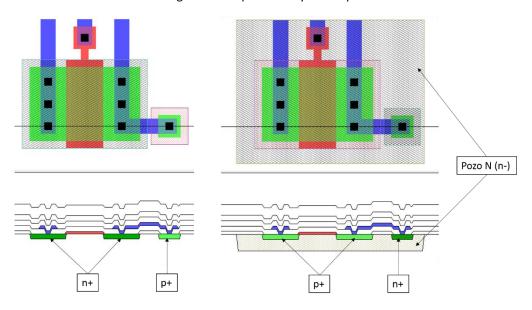

| Figura 3-9. Secuencia de diseño FGMOS-N.                                                            | 74   |

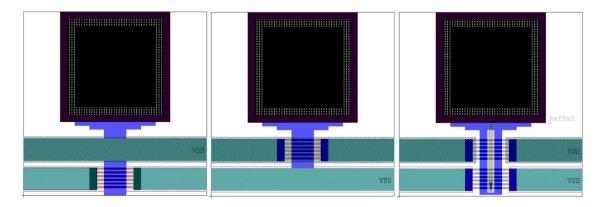

| Figura 3-10. Pads de conexión a VSS, a VDD y de tensión de referencia                               |      |

| Figura 3-11. I/Opad, NC pad, padless y padless corner.                                              | 75   |

| Figura 3-12. Celdas de FGMOS y de membranas de 100, 120 y 150 $\mu m$                               | 75   |

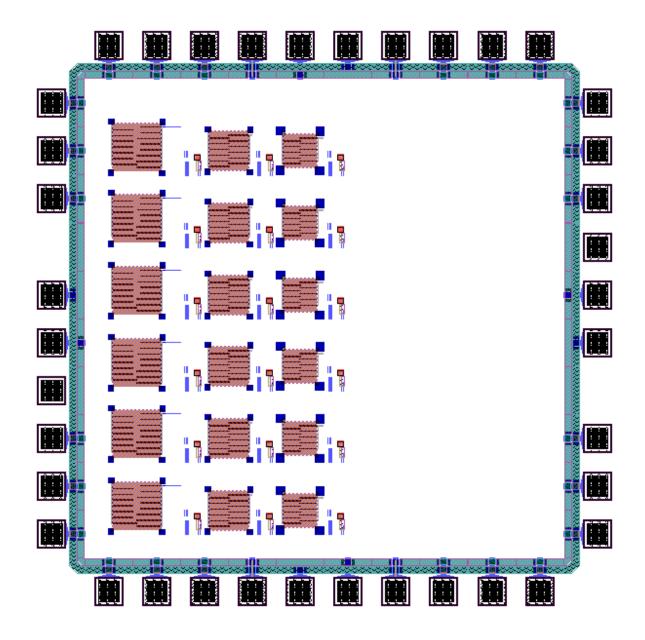

| Figura 3-13. Propuesta básica de PadFrame.                                                          | 76   |

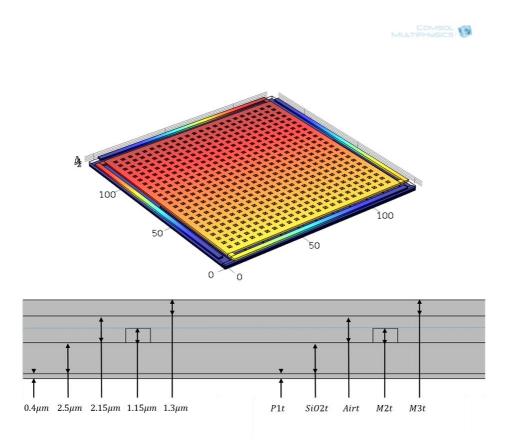

| Figura 3-14. Modelo geométrico para simulación multifísica                                          | 77   |

| Figura 4-1. Dimensiones y capas del modelo mecánico equivalente                                     |      |

| Figura 4-2. Selecciones explicitas de superficie.                                                   | 81   |

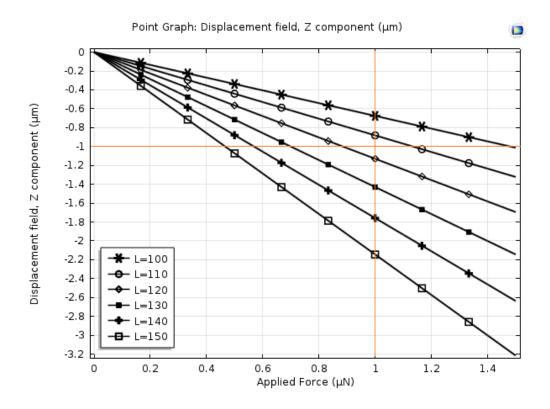

| Figura 4-3. Desplazamiento en z en función de la fuerza aplicada                                    | 82   |

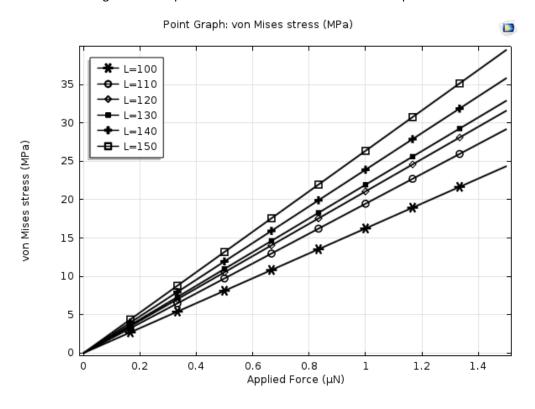

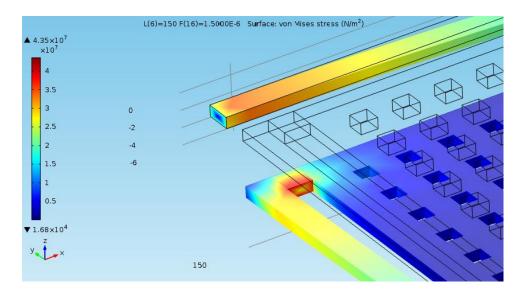

| Figura 4-4. Esfuerzo Von Mises en función de la fuerza aplicada                                     | 82   |

| Figura 4-5. Esfuerzos von Mises máximos en función de la fuerza aplicada                            | 83   |

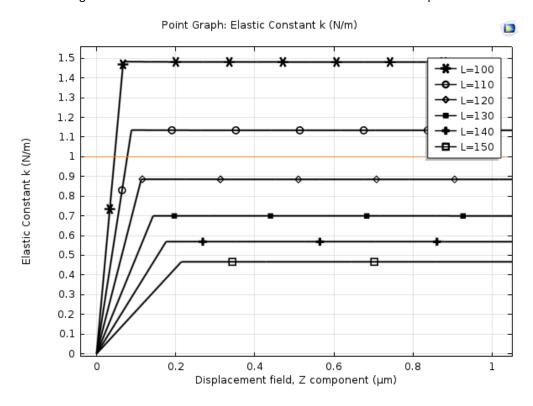

| Figura 4-6. Constante elástica k.                                                                   | 83   |

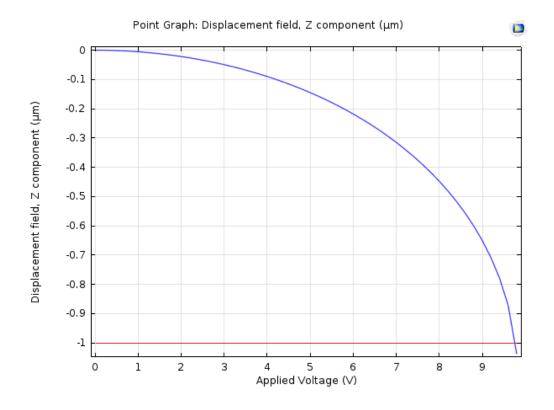

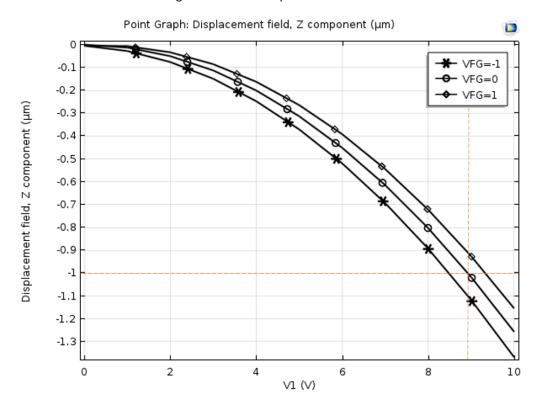

| Figura 4-7.Desplazamiento en función del voltaje aplicado (membrana 120 micras)                     | 84   |

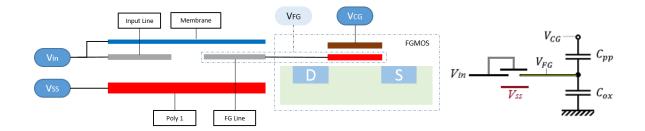

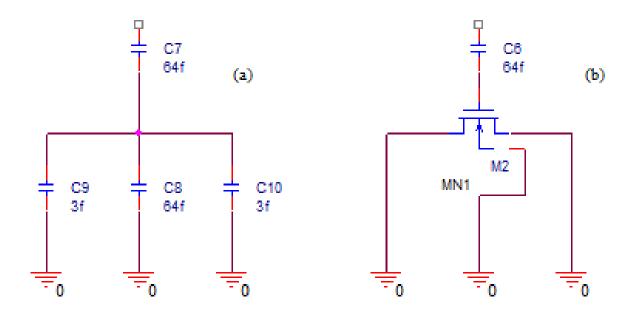

| Figura 4-8.Circuito equivalente MEMS.                                                               | 85   |

| Figura 4-9. Desplazamiento en función del potencial de compuerta flotante                           | 85   |

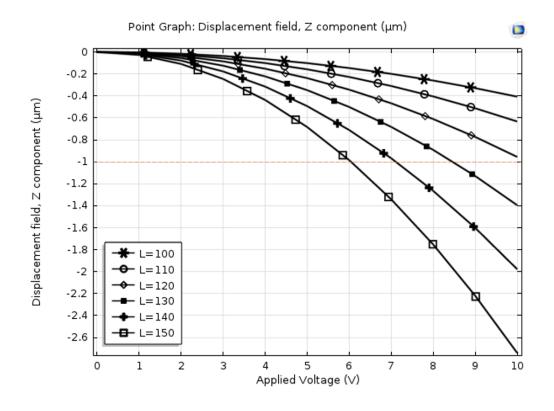

| Figura 4-10. Desplazamiento en función de las dimensiones de la membrana de prueba                  | 86   |

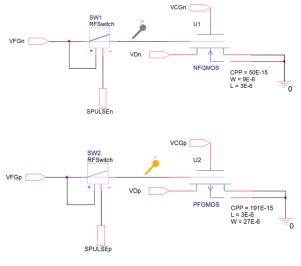

| Figura 4-11. Circuitos FGMOS equivalentes de prueba.                                                | 87   |

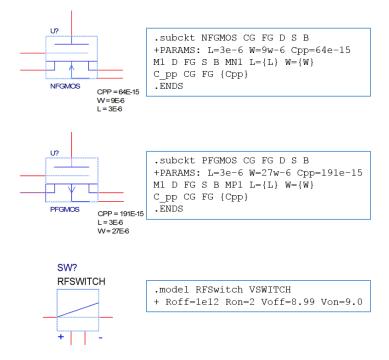

| Figura 4-12. Componentes SPICE creados.                                                             | 88   |

| Figura 4-13. Circuito de estímulo para los transistores FGMOS.                                      | 88   |

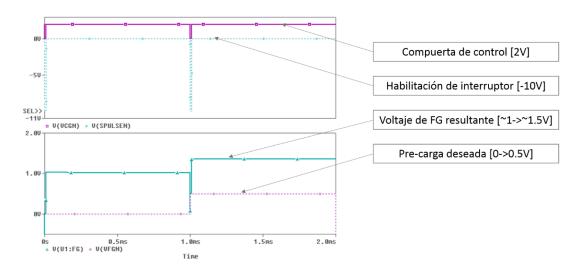

| Figura 4-14. Simulación Clocked NeuMOS inicial                                                      | 89   |

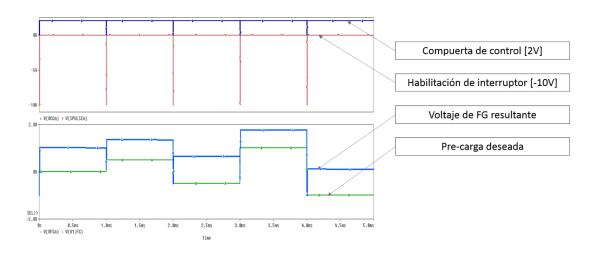

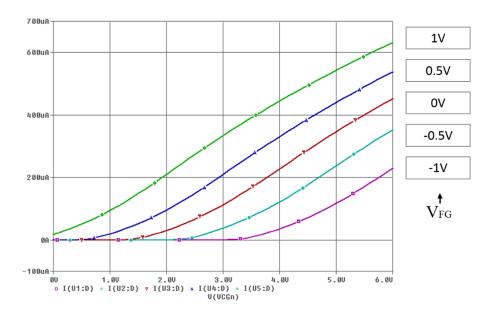

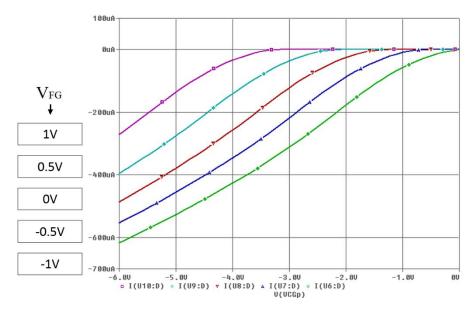

| Figura 4-15. Comportamiento del transistor FGMOS tipo N                                             |      |

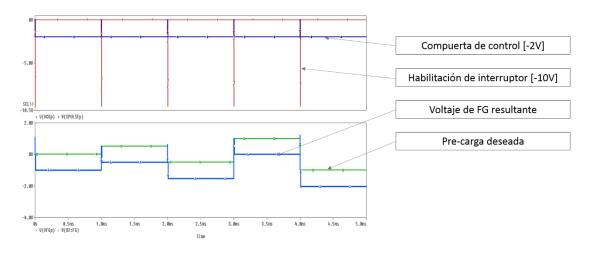

| Figura 4-16. Comportamiento del transistor FGMOS tipo P                                             | 90   |

| Figura 4-17. Curva de transconductancia del transistor FGMOS tipo N en función de la precarga.      | . 91 |

| Figura 4-18. Curva de transconductancia del transistor FGMOS tipo P en función de la precarga       | 91   |

Diseño de un interruptor de RF-MEMS como alternativa para el funcionamiento cuasi-flotante del FGMOS

### Índice de tablas

| Tabla 1-1. Comparativa entre los procesos de fabricación microelectrónico y de micro | osistemas 5 |

|--------------------------------------------------------------------------------------|-------------|

| Tabla 1-2. MEMS clasificados por funcionamiento                                      | 7           |

| Tabla 1-3. MEMS clasificados por proceso de fabricación                              | 7           |

| Tabla 1-4. MEMS clasificados por tipo de energía principal                           | 8           |

| Tabla 1-5. Propiedades del óxido de silicio                                          | 12          |

| Tabla 1-6. Resistividad eléctrica en los materiales de fabricación                   | 13          |

| Tabla 1-7. Micromaquinado volumétrico vs. micromaquinado superficial                 | 19          |

| Tabla 1-8. Micromaquinado: Ataque seco vs. ataque húmedo                             | 19          |

| Tabla 1-9. Velocidad de ataque en el micromaquinado volumétrico                      | 21          |

| Tabla 1-10. Principales características del capacitor de placas paralelas            | 30          |

| Tabla 1-11. Simulación multifísica                                                   | 33          |

| Tabla 2-1. Ciclo de trabajo del microinterruptor electrostático                      | 36          |

| Tabla 2-2. Corriente de drenador en el FGMOS                                         | 64          |

#### Resumen

El presente trabajo aborda de manera teórica y por medio de procedimientos matemáticos y simulaciones computarizadas los aspectos de diseño estructural, comportamiento mecánico y caracterización eléctrica de los interruptores electromecánicos a pequeña escala, en adelante también llamados interruptores MEMS o simplemente interruptores. Asimismo, este proyecto pretende crear conciencia sobre los alcances y limitaciones en los procesos de fabricación de circuitos integrados y sistemas microelectromecánicos con la intención de plantear nuevos retos en el ámbito académico e industrial a corto y mediano plazo.

Si bien el caso de estudio en este trabajo es el de analizar las características de los dispositivos micrométricos involucrados, la aplicación principal y cuyas necesidades se busca cubrir, es la de alimentar con carga eléctrica la compuerta flotante de un transistor FGMOS proveyendo a la terminal de compuerta flotante de una trayectoria física de transporte de carga, misma que puede ser interrumpida de manera mecánica actuando sobre el interruptor electromecánico. Esta es una alternativa para abordar el principio de operación cuasi-flotante de la compuerta flotante del FGMOS, de tal forma que se eliminan o reducen las fugas de corriente característicos al emplear un MOS convencional como interruptor entre la fuente de corriente continua y la compuerta flotante.

Cabe mencionar que los transistores de compuerta flotante FGMOS son una variante de los transistores MOS (metal-óxido-semiconductor) convencionales, cuyas características permiten extender y abarcar diversas aplicaciones de la electrónica analógica como lo son medidores de aceleración, sensores de reacción química y gases, e incluso, aplicaciones de redes neuronales artificiales; sin embargo, la tecnología de fabricación estándar de circuitos integrados presenta problemas en el manejo de la carga electrostática fija en la terminal de compuerta, la cual deteriora el comportamiento de los dispositivos. Es por esto que este trabajo propone, evalúa y compara distintas configuraciones de interruptores electromecánicos, los cuales de manera intrínseca restringen la aparición de cargas no deseadas.

#### **Abstract**

In this work, taking advantage of mathematical procedures and computer simulations, a wide theoretical analysis is developed on matter of MEMS switches. The design project also considers the physical limitations due to the standard manufacturing processes of integrated circuits and microelectromechanical systems, aiming at new challenges and applications for the MEMS devices.

Even though this work emphasizes the characteristics of the MEMS devices involved, the main application for which necessities this work is intended are related to the charge and discharge mechanism in the floating gate terminal in FGMOS transistors. The path that electric current follows to the gate might be interrupted by using an electromechanical switch controlled by the adjacent integrated circuit.

FGMOS are an specific type of MOS transistor which characteristics allows to cover many analog electronic applications, for example, accelerometers and artificial neural networks; anyway, the current standard manufacturing technology on integrated circuits involves some non-desirable issues on the managing of static charge in the gate terminal, that's why this work proposes and evaluates some MEMS switch configurations, that due to its architecture avoid the undesired charges.

### Objetivos

#### Objetivo General

Establecer un diseño de interruptor electromecánico de dimensiones micrométricas basado en la tecnología MEMS y con apego a las reglas de diseño y procesos de fabricación de la tecnología estándar de circuitos integrados CMOS de 0.5µm; asimismo, validar el diseño a través de los modelos eléctricos y matemáticos pertinentes, así como el funcionamiento por medio de herramientas de simulación multifísica de elemento finito.

#### Objetivos Particulares

- Proponer y evaluar la estructura mecánica para el interruptor microelectromecánico, identificando las propiedades y ventajas de las diferentes capas de los materiales que componen al circuito integrado.

- Obtener un modelo de simulación eléctrica adecuado para la implementación del interruptor microelectromecánico como medio de carga y descarga de la compuerta flotante en aplicaciones con transistores FGMOS.

- Diseñar el circuito integrado adjunto que permita la interacción de los equipos de alimentación, estímulo y medición con el microactuador.

- Estimar el desempeño del microinterruptor en su posible aplicación para la operación del FGMOS cuasi-flotante.

#### Justificación

Los dispositivos FGMOS cuyo diseño y fabricación parten de la tecnología estándar de circuitos integrados CMOS de 0.5µm, presentan problemas de concentración de carga en la terminal flotante. Dado que esta región de material semiconductor está, por definición, aislada eléctricamente del resto del circuito, una vez que el exceso de carga eléctrica ha llegado por efecto túnel o defectos de fabricación, es de gran dificultad extraerla o minimizar sus efectos, que en este caso afectan de manera significativa al punto de operación y voltajes de umbral del transistor. Es por esto que se propone como alternativa de solución, un interruptor microelectromecánico que sirva de mecanismo de carga y descarga de la compuerta flotante. Por otra parte, considerando el traslape existente entre la microelectrónica y la tecnología MEMS y dentro de la experiencia que se está intentando ganar dentro del Grupo de Sistemas VLSI de la SEES, se busca incrementar el conocimiento alrededor de los actuadores microelectromecánicos y sus potenciales aplicaciones.

#### 1. Introducción

Los sistemas microelectromecánicos MEMS (MicroElectroMechanical Systems) conforman un área de la Ingeniería Eléctrica estrechamente relacionada con la Microelectrónica y el Diseño de Circuitos Integrados (CIs). En general, los MEMS pueden ser considerados microsistemas de sensores y/o actuadores embebidos dentro de las diversas capas de materiales que existen en un circuito integrado aunque, de manera particular, el grupo de dispositivos conocido como MEMS se caracteriza por contener al menos un elemento sensible o móvil de dimensiones microscópicas.

Por definición, el apelativo MEMS sugiere la interacción entre fuerzas eléctricas y mecánicas, sin embargo, no todos los dispositivos y sistemas que usualmente reconocemos como MEMS involucran estas dos variables, siendo que una gran parte de los mismos son, en al menos parte del sistema, puramente mecánicos, hidrodinámicos, termoeléctricos, piezoeléctricos o electromagnéticos.

Los sistemas microelectromecánicos (MEMS) han logrado una muy amplia y creciente penetración en el mercado de la electrónica, estando hoy en día presentes en prácticamente todos los ámbitos de la vida cotidiana, incluyendo por supuesto, el entretenimiento, la seguridad y control de vehículos, la industria militar y un sinfín de aplicaciones académicas y de apoyo a la investigación. Un caso especialmente aprovechado en aplicaciones y prototipos académicos son los acelerómetros MEMS; su presentación como unidad modular (Figura 1-1) les permite trabajar en integración con otros sistemas y así establecer el esquema de control y estabilidad en móviles, vehículos y brazos robóticos articulados.

Figura 1-1. Acelerómetro MEMS de uso principalmente académico Sparkfun ADXL345.

Diseño de un interruptor de RF-MEMS como alternativa para el funcionamiento cuasi-flotante del FGMOS

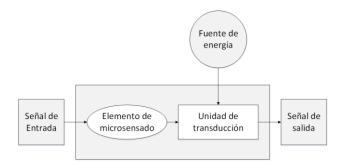

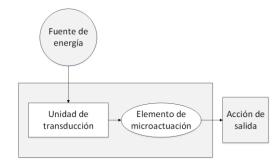

Al igual que su contraparte macroscópica, estos sistemas electromecánicos de pequeñas dimensiones pueden fácilmente identificarse por el rol que juegan dentro del sistema electrónico y por la estructura que comparten sus diferentes variantes. Ya sea como microsensores o como microactuadores, el núcleo de un sistema microelectromecánico consta de dos partes principales, un elemento de sensado o actuación y una unidad de transducción.<sup>2</sup> En la Figura 1-2 y la Figura 1-3 se esquematizan ambos casos del MEMS básico. Cabe resaltar que los dispositivos MEMS, por su naturaleza interactiva con el medio físico, son sistemas electrónicos inherentemente analógicos, sin embargo, esto no inhibe su capacidad para integrarse con elementos digitales de procesamiento para formar sistemas más versátiles y complejos.

Desde otro punto de vista, podría generalizarse que los sistemas microsensores son aquellos puentes e interfaces entre el mundo físico y el sistema electrónico intérprete, ya sea registrando variaciones en la presión, la temperatura, reacciones químicas, desplazamiento háptico e incluso sutiles cambios en el campo eléctrico, por mencionar algunas aplicaciones.

Figura 1-2. Elementos de un sistema microsensor básico.

Figura 1-3. Elementos de un sistema microactuador básico.

Figura 1-4. Microfotografía SEM de un microactuador (manipulador robótico).<sup>3</sup>

Por otra parte, los sistemas microactuadores están más estrechamente relacionados con el control de señales de energía o información. Este es el caso de los interruptores eléctricos u ópticos, también se han aprovechado como sistemas de propulsión motriz o como efectores finales en mecanismos (Figura 1-4) y robots de muy pequeñas dimensiones.

#### 1.1. Antecedentes

Los MEMS surgen de manera natural como una alternativa de estudio durante la incansable búsqueda por obtener mejores métodos de fabricación de circuitos integrados. La necesidad de métodos de depósito y decapado de materiales precisos y confiables permitió a investigadores de todo el mundo idear nuevas estructuras para crear dispositivos interesantes. En particular, la entonces nueva habilidad para liberar capas del circuito integrado de sus respectivos soportes mecánicos permitió sugerir una variedad de aplicaciones donde una diminuta masa móvil y sus interacciones con el circuito electrónico circundante pudieran aprovecharse para la detección de fuerzas o señales presentes en el sistema, así como para la ejecución de tareas motrices, control de microfluidos, etc.

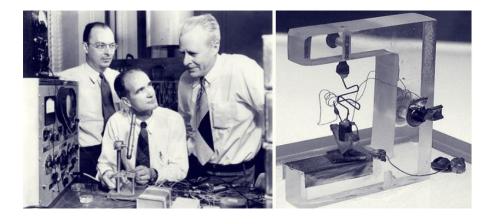

La historia de los sistemas microelectromecánicos está escrita en términos de la tecnología de semiconductores y la industria microelectrónica. Shockley, Bardeen y Brattain (1947) son reconocidos como los desarrolladores del primer transistor funcional, fabricado a partir de un cristal de germanio (Figura 1-5). Este suceso puede ser considerado el nacimiento de una de las mayores industrias a nivel global, disparando una vertiginosa competencia por obtener el conocimiento científico y técnico en el manejo y perfeccionamiento de los materiales semiconductores. Muestra de esto son las diversas patentes que se presentarían en la siguiente década, las cuales incluyen al transistor de punto-contacto (Westinghouse, 1948), el transistor de superficie-barrera (Philco, 1953), el primer transistor comercial de silicio (Bell Labs,

1956) y en especial el primer circuito integrado monolítico de germanio (Texas Instruments, 1958) con el que Kilby se hizo años después acreedor al Premio Nobel de física. Este primer concepto de circuito integrado monolítico sería prontamente mejorado por Noyce (Fairchild Semiconductors, 1959) quien obtuvo mejores resultados haciendo uso de cristales de silicio.

La difícil y costosa obtención de cristales de silicio de buena calidad semiconductora fue una fuerte limitante para la fabricación de dispositivos electrónicos a mediados del siglo XX. Sin embargo, el desarrollo en ese rubro no ha cesado y hoy en día por su abundancia y calidad, el silicio se ha posicionado como la materia prima principal y de más amplio uso en la industria microelectrónica.

Más allá del silicio y en conjunto con éste, una gran variedad de elementos y compuestos, tanto semiconductores como conductores y dieléctricos, son parte de los circuitos integrados modernos. Dichos componentes suelen presentarse por capas en la mayoría de los procesos industriales de fabricación como lo es el de la tecnología CMOS estándar, la cual es objeto de estudio en el presente trabajo y se abordará en las secciones siguientes. La generación de capas de distintos materiales involucra diversos métodos de depósito y decapado, a los cuales la aparición de los MEMS está relacionada. Algunos de los MEMS más sencillos pueden constar únicamente de porciones de material metálico o semiconductor en configuración de viga con empotramiento simple, caso que llega a presentarse cuando el activo decapante profundiza más de lo deseado, retirando el soporte mecánico alrededor de cierto elemento circuital y cuyas nuevas características y comportamiento son de nuestro interés.

Figura 1-5. John Bardeen, William Shockley y Walter Brattain en los laboratorios Bell, 1948.

Tabla 1-1. Comparativa entre los procesos de fabricación microelectrónico y de microsistemas

| Microelectrónica                                          | Sistemas microelectromecánicos                    |

|-----------------------------------------------------------|---------------------------------------------------|

| Utiliza silicios cristalinos monolíticos,                 | Silicio cristalino, compuestos del silicio, GaAs, |

| compuestos del silicio y plásticos.                       | cuarzo, polímeros y metales.                      |

| Transmite señales eléctricas para aplicaciones            | Gran variedad de funciones biológicas,            |

| eléctricas específicas.                                   | químicas, ópticas, electromecánicas, etc.         |

| Estructura mecánica estacionaria, usualmente              | Puede incluir componentes móviles y               |

| planar.                                                   | complejas estructuras tridimensionales.           |

| Motivos y patrones complejos con alta                     | Motivos y patrones relativamente sencillos por    |

| densidad de integración.                                  | encima del sustrato.                              |

| Relativamente pocos elementos a ensamblar.                | Relativamente muchos elementos a ensamblar.       |

| Aislamianta manasta al ambienta sinoundanta               | Interfaces de sensado en contacto con el          |

| Aislamiento respecto al ambiente circundante.             | ambiente circundante.                             |

| Madagas ag las grato delectos de diseño                   | Metodologías de diseño y estándares               |

| Madurez en las metodologías de diseño.                    | incipientes.                                      |

| Gran número de interconexiones y trayectorias.            | Pocas interconexiones y trayectorias.             |

| Estándares industriales disponibles.                      | Ausencia de estándares industriales generales.    |

| Producción masiva.                                        | Producción limitada acorde a las necesidades.     |

| Técnicas de fabricación probadas y                        | Uso de diversas técnicas de fabricación de        |

| extensamente documentadas.                                | microelectrónica.                                 |

| Técnicas de manufactura probadas y                        | Diversas técnicas de manufactura.                 |

| extensamente documentadas.                                | Diversas tecnicas de manufactura.                 |

| Tecnología de encapsulado relativamente bien establecida. | Tecnología de encapsulado incipiente.             |

Se puede deducir entonces que un proceso controlado de decapado, el cual es selectivo y en muchos casos preferentemente anisotrópico, es la base de la fabricación de MEMS. Más aún, vale la pena resaltar las diferencias y particularidades que presentan un proceso de fabricación microelectrónica estándar y un proceso de fabricación de microsistemas. A continuación se presenta una comparativa entre ambos procesos desde el enfoque de la tecnología de fabricación, evolución industrial y aplicaciones. Es esencial reconocer las diferencias entre el diseño y fabricación de los microsistemas respecto a la tecnología microelectrónica y de circuitos integrados, las cuales están descritas en la Tabla 1-1<sup>4</sup>.

En la actualidad, al igual que cualquier circuito integrado o sistema microelectrónico, por sus reducidas dimensiones y bajos costos unitarios, los MEMS presentan una producción industrial masiva. La primera aplicación con dispositivos MEMS que se integró al mercado a gran escala es la de los sensores de presión. Dichos elementos de medición han ido evolucionando y hoy en día pueden ser encontrados incluso al interior de relojes deportivos y algunos otros instrumentos de medición relacionados. La industria automotriz por su parte, toma MEMS con características de medición de fuerzas inerciales para implementar los más

modernos sistemas de seguridad en los vehículos, siendo un acelerómetro de precisión en conjunto con un sistema digital quienes han protegido por años la integridad de los pasajeros. En otros casos de medición inercial, los giroscopios han resultado efectivos en las aplicaciones de estabilización de imagen en cámaras fotográficas y de video, sistemas de entretenimiento, teléfonos celulares y en la navegación por GPS.

#### 1.1.1. MEMS y su clasificación

Los dispositivos MEMS cuentan con un gran número de aplicaciones, es por ello que existe también una variedad de opciones para clasificarlos. Para fines de este trabajo podemos clasificarlos mediante tres criterios principales:

- MEMS por función principal.

- o MEMS como actuadores.

- MEMS como sensores.

- MEMS por proceso de fabricación.

- o MEMS por micromaquinado superficial.

- o MEMS por micromaquinado volumétrico.

- MEMS por transducción.

- MEMS por fuerzas electrostáticas.

- o MEMS por fuerzas piezoeléctricas.

- MEMS por fuerzas térmicas.

- MEMS por fuerzas magnéticas.

Dada esta clasificación y sus múltiples combinaciones, en este trabajo procedemos a identificar cada una de ellas y encontrar un dispositivo adecuado para la aplicación propuesta.

Como se revisó en la sección introductoria, cuando se les clasifica por su funcionamiento los MEMS pueden ser encontrados como sensores o actuadores. Los dispositivos sensores interactúan directamente con el medio físico circundante y en general, transducen algún tipo de energía de entrada en una señal eléctrica medible. Asimismo, los MEMS que funcionan como actuadores utilizar recursos eléctricos para realizar un desplazamiento mecánico. Debemos considerar que en ambos casos, ya sea la entrada de energía que se recibe o la

acción mecánica que se realice, son señales de muy pequeña magnitud desde el punto de vista macroscópico. Sin embargo, dado el escalamiento de las fuerzas en relación a las dimensiones geométricas del dispositivo, las fuerzas electrostáticas, la presión atmosférica y otros tipos de energía toman relevancia sobre el comportamiento del dispositivo. Algunas de las posibles aplicaciones que se encuentran basadas en los microsensores o microactuadores, se presentan en la Tabla 1-2.

Los dispositivos MEMS también pueden clasificarse por el proceso de fabricación necesario para obtenerlos. En específico, por los alcances de los métodos de decapado, los cuales pueden eliminar ya sea las capas superficiales de polisilicio, metales y óxidos o en otros casos, al sustrato mismo (ver Tabla 1-3). A estas dos variantes se les conoce como *micromaquinado superficial* y *micromaquinado volumétrico* respectivamente y sus propiedades se abordarán más adelante.

Tabla 1-2. MEMS clasificados por funcionamiento.

| Clasificación   | Energía                                      | Aplicaciones                                                                                                                                       |  |

|-----------------|----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                 | Presión en fluidos                           | <ul> <li>Medición de presión atmosférica;</li> <li>Presión de fluidos en ductos y turbomáquinas;</li> <li>Dispositivos neumáticos; etc.</li> </ul> |  |

| Microsensores   | Campo eléctrico,<br>magnético y capacitancia | Acelerómetros, giroscopios y brújulas electrónicas:                                                                                                |  |

|                 | Energía térmica                              | <ul> <li>Sensado de temperatura;</li> <li>Detección de reacciones químicas y radiación; etc.</li> </ul>                                            |  |

| Microactuadores | Energía electromecánica                      | <ul> <li>Interruptores electromecánicos y ópticos;</li> <li>Micromanipuladores robóticos;</li> <li>Control de microfluidos; etc.</li> </ul>        |  |

|                 | Energía térmica                              | <ul><li>Interruptores bimetálicos;</li><li>Control de reacciones químicas; etc.</li></ul>                                                          |  |

Tabla 1-3. MEMS clasificados por proceso de fabricación.

| Clasificación              | Ataque principal              | Aplicaciones                                                             |

|----------------------------|-------------------------------|--------------------------------------------------------------------------|

| Micromaquinado superficial | Sustrato (silicio cristalino) | Eliminar las restricciones mecánicas entre las capas de depósito.        |

|                            |                               | Generar espacios profundos y libres por debajo de las capas de depósito. |

|                            |                               | debajo de las capas de deposito.                                         |

Tabla 1-4. MEMS clasificados por tipo de energía principal.

| Clasificación                    | Fenómenos principales                                                        | Aplicaciones                                                                            |  |

|----------------------------------|------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|--|

| MEMS por fuerzas electrostáticas | <ul><li>Capacitancia</li><li>Campo eléctrico</li></ul>                       | Acelerómetros, giroscopios, interruptores electrostáticos, varactores, microactuadores. |  |

| MEMS por fuerzas piezoeléctricas | <ul><li>Piezoelectricidad</li><li>Estrés mecánico</li></ul>                  | Sensores de presión, micrófonos, acelerómetros.                                         |  |

| MEMS por fuerza piezoresistivas  | <ul><li>Piezoresistividad</li><li>Estrés mecánico</li></ul>                  | Sensores de presión (esfuerzo de extensión y compresión).                               |  |

| MEMS por fuerzas<br>térmicas     | <ul><li>Efecto Joule</li><li>Transferencia de calor por conducción</li></ul> | Sensores de reacción química, sensores de temperatura, microactuadores bimetálicos.     |  |

| MEMS por fuerzas magnéticas      | <ul><li>Inductancia</li><li>Campo magnético</li></ul>                        | Detectores de campo magnético.<br>Microactuadores.                                      |  |

Por último, para fines de este trabajo podemos clasificar a los dispositivos microelectromecánicos por el tipo de energía y fuerzas que se transducen y finalmente se aprovechan como una señal eléctrica, como se muestra en la Tabla 1-4. Los MEMS de fuerzas piezoeléctricas y fuerzas piezoresistivas detectan los cambios que el estrés mecánico produce en el campo eléctrico y resistencia eléctrica, respectivamente, en un material de prueba dado.

Los MEMS de fuerzas electrostáticas, también llamados capacitivos, utilizan un fenómeno inherente a cualquier dispositivo electrónico como lo son las capacitancias y campos eléctricos que aparecen entre las capas de material y a lo largo de todas sus superficies. A través de ligeras variaciones en la capacitancia, ya sea de placas paralelas o de franja lateral, se pueden detectar los desplazamientos relativos entre placas, para detectar movimiento o aceleración, por ejemplo.

Otro tipo de MEMS convencionales son los de fuerzas térmicas; estos pueden sacar ventaja del efecto Joule como método de actuación mecánica o como herramienta para detección indirecta de otros parámetros. En última instancia, consideraremos a los MEMS de fuerzas magnéticas, que si bien son de difícil manufactura y aplicaciones escasas, ofrecen un amplio territorio para la investigación básica. Esto no sucede así en el mundo macroscópico, en el cual la actuación magnética es una de las más ampliamente utilizadas.

#### 1.1.2. Tecnología CMOS estándar

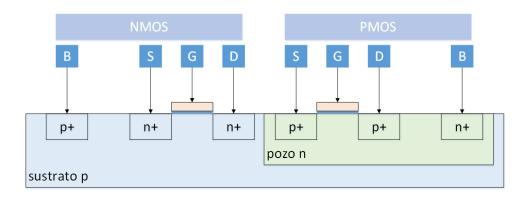

La tecnología CMOS estándar es aquella que une elementos MOS, en especial transistores MOS canal N y canal P en el mismo sustrato como los mostrados en la Figura 1-6, consiguiendo así, la integración de algunos dispositivos sencillos como inversores y amplificadores operacionales y tan complejos como lo son las unidades aritmético-lógicas (ALU) presentes en los microprocesadores.

La estandarización de procesos en la industria electrónica es una herramienta importante también en el ámbito académico, puesto que permite desarrollar prototipos de investigación siguiendo procedimientos y metodologías bien establecidas. Siguiendo el proceso de desarrollo eventualmente se solicita la fabricación de los circuitos y dispositivos previamente diseñados, analizados y simulados, para finalmente proceder a una caracterización física de los parámetros eléctricos en el laboratorio.

En el caso particular de este trabajo, la metodología a utilizar es la tecnología CMOS estándar de 0.5μm bajo el proceso OnSemi C5N<sup>5</sup> (antes conocido como AMIS) del proveedor MOSIS<sup>6</sup>. Los parámetros tecnológicos propios de esta tecnología definen las reglas de diseño y materiales disponibles para el proceso de fabricación y pueden consultarse en la sección de apéndices del presente documento. Cabe aclarar que al ser esta tecnología específica para la fabricación de circuitos integrados CMOS, se pretende adaptar sus características y propiedades para nuestro propósito, de tal manera que se puedan obtener estructuras tridimensionales típicas de los MEMS, mediante un post-proceso de micromaquinado que se deberá realizar posterior a la fabricación del dado o chip.

Figura 1-6. Diagrama de transistores NMOS y PMOS en la tecnología CMOS estándar.

Esta aproximación tiene sus limitaciones, debido a que las dimensiones y características de las diferentes capas no están concebidas para desempeñarse como sensores o actuadores. Sin embargo, esto no impide que mediante estrategias de diseño, se puedan idear estructuras que puedan ser liberadas mediante un proceso de micromaquinado (ya sea superficial o volumétrico), aprovechando las propiedades enmascarantes de las capas usadas en la fabricación de dispositivos CMOS, que fundamentalmente son las mismas que se emplean en tecnologías dedicadas a la obtención de estructuras MEMS. También vale la pena comentar que estas últimas tecnologías, son adecuadas para fabricar estructuras MEMS, pero no ofrecen una plataforma para la integración de elementos electrónicos como lo hace la tecnología CMOS. Aun así, es posible hacer una adaptación para acoplar ambas tecnologías, con lo que se obtiene la llamada tecnología CMOS-MEMS. Este es el objetivo del diseño que se presenta y desarrolla en el presente trabajo.

Una manera conveniente de identificar a las diversas tecnologías de fabricación de circuitos integrados, así como sus ventajas, desventajas y alcances, es mediante los siguientes parámetros:

- Ancho de canal: esta cantidad expresa el mínimo de separación que puede haber entre el drenador y la fuente de un transistor MOS dado; se debe a las limitantes tecnológicas del proceso y el dato ofrece una forma indirecta para conocer el grado de integración del circuito definitivo, es decir, la cantidad de elementos integrados por área en la oblea de silicio. En nuestro caso de estudio, la tecnología de fabricación utilizada corresponde a un ancho de canal mínimo de 0.5μm.

- Materiales de fabricación<sup>7</sup>: si bien la gran mayoría de las aplicaciones en la electrónica integrada se desarrollan sobre obleas de silicio cristalino, éste no es el único material que forma parte del proceso ni del producto final. Mencionando algunos de los materiales que conforman a los circuitos integrados podemos encontrarnos con metales como el aluminio (Al), el cobre (Cu), el oro (Au) y la plata (Ag). Por otra parte, algunas aplicaciones requieren de compuestos orgánicos y polímeros, también es común utilizar nitruros y carburos y por supuesto, diversos compuestos del silicio, tales como el silicio policristalino, dióxido de silicio (SiO<sub>2</sub>),

carburo de silicio (SiC) y nitruro de silicio (Si $_3$ N $_4$ ). Cada uno de estos cumple con diferentes funciones dentro del proceso o como parte de la estructura terminal. En especial, los compuestos del silicio se utilizan de muy diversas formas, como se explica a continuación:

- Silicio cristalino (Si): Conforma la oblea de material cristalino, la cual da soporte mecánico a la estructura y contiene regiones a las que por medio de métodos de difusión e implantación iónica se le dan las propiedades eléctricas deseadas. La región activa es donde ocurren los principales fenómenos de transporte dentro del material semiconductor de un dispositivo dado. En el caso de los transistores MOS, son regiones de material cristalino impurificado que para efectos del dispositivo, trabajan como fuente o drenador. Cabe señalar que el silicio cristalino de la oblea contiene una impurificación más ligera que la región activa para poder funcionar como sustrato de los dispositivos. En general, si el sustrato tiene una impurificación tipo p, debe construirse una región tipo n llamada pozo en la cual se construyan los dispositivos canal p. A las aplicaciones que involucran pozo n y por tanto ambos tipos de transistor PMOS y NMOS, se le conoce como tecnología CMOS o MOS complementaria.

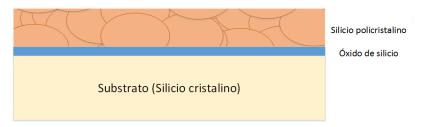

- Silicio policristalino (p-Si): Comúnmente llamado "polisilicio" o "poly", es un material de silicio puro, sin embargo, su estructura atómica no es totalmente cristalina a lo largo de su extensión (Figura 1-7). Se conforma de un aglomerado de pequeños monocristales por lo que sus características eléctricas son intermedias entre las de un semiconductor y un dieléctrico. Suele utilizarse como material conductor para construir las compuertas del transistor MOS y en ocasiones es sustituido por metales como el aluminio o el cobre para esta misma tarea. Las razones principales por las que su uso se generalizó son su resistencia a las altas temperaturas del proceso de fabricación y sus características eléctricas similares a las del sustrato que permiten controlar y obtener valores deseables en el voltaje de umbral de los transistores MOS.

Figura 1-7. Primera capa de polisilicio en el proceso CMOS estándar.

Tabla 1-5. Propiedades del óxido de silicio.

| Propiedades                              | Valores        |

|------------------------------------------|----------------|

| Densidad, g/cm <sup>3</sup>              | 2.27           |

| Resistividad, Ω·cm                       | $\geq 10^{16}$ |

| Permitividad relativa                    | 3.9            |

| Punto de fusión, °C                      | ~1700          |

| Calor específico, J/g-°C                 | 1.0            |

| Conductividad térmica, W/cm-°C           | 0.014          |

| Coeficiente de expansión térmica, ppm/°C | 0.5            |

- Óxido de silicio (SiO<sub>2</sub>): Es un compuesto que aparece de manera natural en la superficie expuesta de la oblea, sin embargo su espesor y velocidad de crecimiento pueden controlarse de manera industrial bajo condiciones de temperatura y humedad específicas. Es utilizado como capa de protección y aislamiento eléctrico entre las regiones activas y capas conductoras que forman a los dispositivos. Permite acoplar diversas capas de material una sobre otra por encima de la superficie de la oblea, extinguiendo casi por completo las posibilidades de corto circuito entre capas y dispositivos. Las propiedades más representativas del óxido de silicio son mostradas en la Tabla 1-5<sup>8</sup>.

- Carburos y nitruros de silicio (SiC, Si<sub>3</sub>N<sub>4</sub>): Son compuestos altamente resistentes a la oxidación, a las altas temperaturas y a la difusión de otras partículas como el agua o el sodio. Es por esto que suelen utilizarse como materiales de pasivación y protección. En especial el nitruro de silicio es considerado una mascarilla efectiva para el decapado volumétrico profundo en la fabricación de MEMS, protegiendo a los dispositivos del ataque.

- Capas de materiales disponibles: Todos los procesos de fabricación estándar se basan en tecnología planar, la cual consiste en generar dispositivos e interconectarlos a través de capas paralelas de materiales apiladas una sobre otra por encima del sustrato. Para hacer efectiva esta técnica se ha desarrollado una gran variedad de procesos fotolitográficos haciendo posible la generación de motivos impresos demarcando las dimensiones de los dispositivos en cada una de las capas y los espacios para las interconexiones entre ellos.

- Resistividad: Una de las propiedades físicas más relevantes en la fabricación de electrónica integrada y dispositivos MEMS es la resistividad. Esta propiedad puede ayudar a determinar las dimensiones del dispositivo para efectos de controlar una corriente eléctrica determinada. En otros casos puede determinar incluso el proceso tecnológico necesario para el desarrollo del prototipo. La Tabla 1-6 muestra una clasificación de los materiales en términos de su resistividad<sup>9</sup>.

Tabla 1-6. Resistividad eléctrica en los materiales de fabricación.

| Materiales                           | Resistividad eléctrica aproximada ρ,<br>Ω·cm | Clasificación |

|--------------------------------------|----------------------------------------------|---------------|

| Plata (Ag)                           | 10 <sup>-6</sup>                             |               |

| Cobre (Cu)                           | $10^{-5.8}$                                  | Conductor     |

| Aluminio (Al)                        | $10^{-5.5}$                                  | Conductor     |

| Platino (Pt)                         | $10^{-5}$                                    |               |

| Germanio (Ge)                        | $10^{-3} - 10^{1.5}$                         |               |

| Silicio (Si)                         | $10^{-3} - 10^{4.5}$                         | Semiconductor |

| Arseniuro de Galio (GaAs)            | $10^{-3} - 10^{8}$                           | Semiconductor |

| Fosfuro de Galio (GaP)               | $10^{-2} - 10^{6.5}$                         |               |

| Óxido de Silicio (SiO <sub>2</sub> ) | 10 <sup>9</sup>                              |               |

| Vidrio                               | $10^{10.5}$                                  | Aislante      |

| Diamante                             | 10 <sup>14</sup>                             | - Instanto    |

| Cuarzo                               | $10^{18}$                                    |               |

Figura 1-8. Esquema de capas de materiales en el proceso OnSemi C5N de 0.5μm.

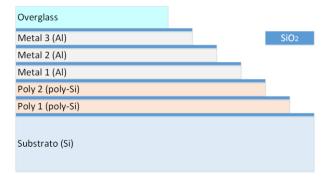

La tecnología OnSemi C5N de MOSIS, es una tecnología 2P3M, en otras palabras, además del sustrato, las capas de óxido aislante, vidrio y pasivación, están disponibles dos capas de polisilicio y tres capas de metal (Al) para utilizarse comúnmente como compuerta del transistor MOS y como pistas conductoras respectivamente, vías y zonas de conexión (pads). La Figura 1-8 muestra un esquema de la distribución de estas capas para esta tecnología.

#### 1.1.3. Compuerta flotante

Lo referente al funcionamiento integral y aplicaciones del transistor de compuerta flotante FGMOS (Floating-Gate MOS) se presenta más adelante en este trabajo dentro del marco del *Capítulo 2: Aspectos teóricos*, sin embargo, en este punto es pertinente resaltar que el término 'compuerta flotante' (FG) se refiere a una de las terminales del dispositivo que se encuentra aislada eléctricamente del resto del dispositivo, completamente encapsulada dentro material dieléctrico, en este caso, una capa de SiO<sub>2</sub> (dióxido de silicio), ampliamente utilizado en el proceso CMOS estándar.

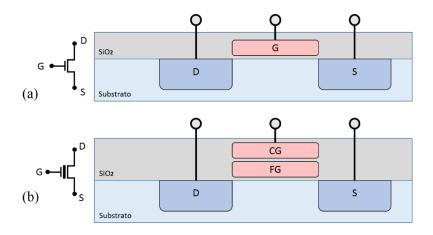

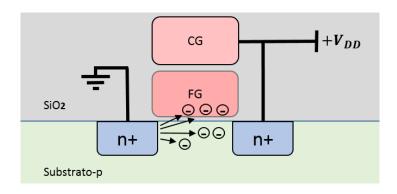

La versión más comúnmente utilizada de la compuerta flotante implementada con tecnología CMOS estándar consta de dos elementos principales, específicamente, dos compuertas trabajando en conjunto sobre el mismo transistor. La Figura 1-9 (a) nos muestra el símbolo y configuración típica de un transistor MOS convencional. En este dispositivo, el voltaje de umbral está establecido en un valor fijo y la operación en los regímenes de acumulación, inversión débil e inversión fuerte, están gobernados directamente por el voltaje aplicado en la compuerta. Dicha compuerta, preferentemente de silicio policristalino (poly), se encuentra aislada de la región activa del sustrato por una muy delgada capa de SiO<sub>2</sub> en el orden de 40nm llamada *óxido de compuerta* y se considera que su acción sobre el sustrato es directa. Por otra parte, la Figura 1-9 (b) muestra el símbolo y arquitectura de un transistor MOS con compuerta flotante.

En este caso, la compuerta que está próxima a la región activa está igualmente formada por la primera capa de polisilicio del proceso, pero se encuentra aislada del resto del circuito, embebida entre capas de material dieléctrico. Por encima de esta compuerta intermedia o *flotante* se deposita una segunda compuerta ya sea con la segunda capa de polisilicio o con

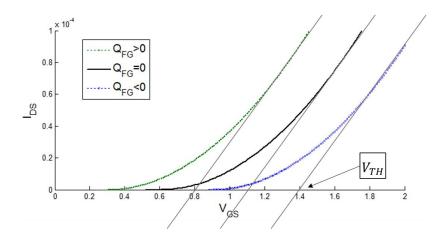

la primera capa de metal del proceso. Sobre esta segunda compuerta, a la que llamamos compuerta de control (CG), se aplica el voltaje de compuerta deseado por medio de una fuente externa, siempre considerando que la carga atrapada en la compuerta flotante produce un corrimiento en el valor final del voltaje de umbral del transistor, ya sea para disminuir o aumentar el voltaje de umbral externo necesario para alcanzar las mismas condiciones de operación que con el transistor MOS convencional, dependiendo en si la carga atrapada es positiva o negativa. La Figura 1-10 muestra el desplazamiento del voltaje de umbral en la característica de transconductancia del transistor FGMOS para distintos valores de carga en la compuerta flotante. Se considera que la aproximación lineal intersecta al eje horizontal en un valor práctico del voltaje de umbral.

Figura 1-9. Configuración de compuerta en transistor (a) MOS convencional (b) FGMOS.

Figura 1-10. Desplazamiento del voltaje de umbral en el FGMOS

Figura 1-11. Inyección por electrones calientes.

Otra cuestión de interés en este trabajo es el método de carga y descarga de la compuerta flotante. Dos de las más comúnmente utilizadas son la inyección de carga por electrones calientes y la inyección por tunelamiento Fowler-Nordheim. El mecanismo de inyección por electrones calientes (ver Figura 1-11) se logra aplicando diferencias de potencial considerables en las terminales de drenador y compuerta (del orden de 25V)<sup>10</sup>, brindándole a las cargas eléctricas que atraviesan el canal la suficiente energía cinética para atravesar el óxido de compuerta. Como es de esperarse, la carga negativa (electrones) es atraída hacia la compuerta aplicando un potencial positivo alto en la misma.

Por otra parte, la Figura 1-12 muestra una simplificación de la configuración típica en un transistor FGMOS con un subsistema de inyección de carga por tunelamiento Fowler-Nordheim. Usualmente la terminal de compuerta flotante se diseña con una extensión más allá de sus dimensiones en el dispositivo para alcanzar una zona de inyección en la cual pueda transferirse carga por medio de una estructura capacitiva con una terminal de voltaje externa. En el punto de inyección se aplica una tensión que provoca el campo eléctrico necesario a fin de producir un tunelamiento Fowler-Nordheim a través del dieléctrico intermedio. Este método permite inducir carga en la compuerta flotante y llevar el potencial eléctrico de la misma hasta el valor deseado si se conocen los parámetros capacitivos de las estructuras de inyección y de compuerta.

La técnica de tunelamiento es efectiva para cargar la compuerta flotante hasta el potencial deseado, sin embargo, la carga que no logra atravesar por completo el material dieléctrico intermedio permanece atrapada siendo de difícil extracción y deteriorando paulatinamente el comportamiento del dispositivo. Más aún, se dice que la inyección por tunelamiento es

autolimitada puesto que conforme la carga eléctrica se incorpora a la compuerta flotante, el voltaje se incrementa ejerciendo una fuerza de repulsión sobre las cargas entrantes. En la Figura 1-13 observamos que cuando el valor de voltaje de inyección se establece la corriente de inyección se detiene debido al equilibrio alcanzado entre el los campos eléctricos del potencial aplicado y de las cargas previamente inyectadas. Efectivas técnicas de carga se han desarrollado mediante pulsos de voltaje a través de estructuras de compuerta cuasi-flotante.

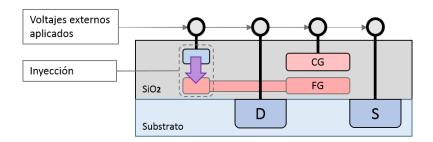

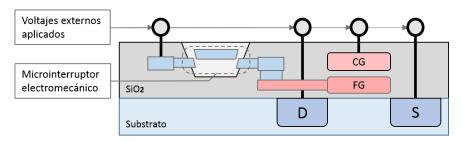

Como parte central de este trabajo y con el objetivo de evitar los inconvenientes del método por tunelamiento, se implementa el diseño y evaluación de un nuevo mecanismo para la carga y descarga de la compuerta flotante de un transistor FGMOS mediante un interruptor electromecánico de dimensiones micrométricas, implementado en las capas de fabricación del proceso CMOS estándar.

Figura 1-12. Inyección de carga por tunelamiento Fowler-Nordheim.

Figura 1-13. Inyección Fowler-Nordheim autolimitada.

Figura 1-14. Inyección de carga mediante un interruptor electromecánico.

La Figura 1-14 muestra un esquema simplificado de la arquitectura propuesta, en el cual, la trayectoria de transporte de carga hacia la compuerta puede ser interrumpida por estímulos eléctricos sobre una interfaz mecánica previamente liberada durante un proceso de micromaquinado superficial.

Alternativamente, la propuesta podría aplicarse hacia el concepto cuasi-flotante del FGMOS, con el cual se precarga transitoriamente la compuerta flotante con un voltaje que ayude a cumplir una función determinada, como se hizo en Sensor inteligente de imágenes en tecnología CMOS con aplicaciones en robótica<sup>11</sup> y Red Neuronal celular programable en tecnología CMOS<sup>12</sup> procedimientos similares fueron también aplicados y detallados en Very low-voltage analog signal processing based on quasi-floating gate transistors<sup>13</sup>, A new family of very low-voltage analog circuits based on quasi-floating-gate transistors<sup>14</sup> y Tunable linear MOS resistors using quasi-floating-gate techniques<sup>15</sup>. En estos trabajos, se emplea un transistor MOS convencional como interruptor, el cual conecta momentáneamente a la compuerta flotante con una fuente de CD para establecer un voltaje inicial de tal forma que se lleva al FGMOS hacia un punto de operación apropiado para cumplir una función en particular. Sin embargo, una desventaja de esta aproximación es que al compartir un mismo sustrato el transistor MOS convencional y el FGMOS, se tiene una trayectoria de fuga por lo que la precarga se tiene que refrescar continuamente mientras se esté operando la celda correspondiente. Esto podría evitarse con interruptor mecánico que abra completamente la trayectoria de fuga y elimine la necesidad del refrescamiento del voltaje cuasi-flotante. La precarga podría realizarse también transitoriamente y esta función se propone hacer con un interruptor similar a los interruptores RF MEMS. Quizá la desventaja que se tendría sería el área empleada para la implementación del interruptor pero no se requerirían circuitos de refrescamiento. Los interruptores RF MEMS originalmente son diseñados para transmitir señales de muy altas frecuencias (del orden de MHz) y en el estudio que se propone en este trabajo se trabajaría a frecuencias muy por debajo de los límites que exigen las aplicaciones en comunicaciones.

#### 1.1.4. Micromaquinado

La característica principal que distingue a los MEMS de entre los dispositivos microelectrónicos es que utilizan estructuras tridimensionales con funciones no sólo electrónicas sino mecánicas y térmicas, por mencionar algunas. Dichas estructuras Diseño de un interruptor de RF-MEMS como alternativa para el funcionamiento cuasi-flotante del FGMOS

tridimensionales se encuentran formando parte del circuito integrado pues comparten la oblea y los materiales de las capas depositadas sobre la misma. En principio, el circuito integrado puede ser funcional y trabajar con señales electrónicas analógicas, digitales o mixtas. Sin embargo, para que un sistema microelectrónico sea considerado como MEMS se requiere generar una estructura tridimensional adyacente, para lo que es preciso aplicar un proceso de micromaquinado, es decir, retirar el material alrededor de nuestra patrón geométrico de interés para aislar la estructura ya sea mecánica o térmicamente del sustrato y con respecto a las demás capas de material.

El proceso de micromaquinado, como método para remover material se presenta en dos variantes generales que atacan ya sea al sustrato o a los materiales depositados en el mismo para lograr diferentes aplicaciones. En otras palabras, la estructura resultante puede clasificarse según haya sido eliminado material en el sustrato o en las capas superiores. La Tabla 1-7 presenta una comparativa entre los procesos de micromaquinado considerando sus aplicaciones.

Tabla 1-7. Micromaquinado volumétrico vs. micromaquinado superficial.

| Proceso de micromaquinado        | Ataque                                              | Objetivo                                                                                                          |

|----------------------------------|-----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|

| Volumétrico<br>(ver Figura 1-15) | Sustrato de silicio cristalino                      | Generar espacios abiertos y membranas por debajo de la superficie de trabajo del sustrato.                        |

| Superficial (ver Figura 1-16)    | Capas de óxido de silicio,<br>polisilicio y metales | Generar membranas, vigas y resortes con los materiales de las capas depositadas sobre la superficie del sustrato. |

Tabla 1-8. Micromaguinado: Ataque seco vs. ataque húmedo.

| Parámetro                            | Ataque seco                             | Ataque húmedo                                                    |  |

|--------------------------------------|-----------------------------------------|------------------------------------------------------------------|--|

| Direccionalidad                      | Buena para la mayoría de los materiales | Relación de hasta 100:1 únicamente en materiales monocristalinos |  |

| Producción automática                | Buena                                   | Pobre                                                            |  |

| Impacto ambiental                    | Bajo Alto                               |                                                                  |  |

| Adherencia de la mascarilla          | No crítica                              | Muy crítico                                                      |  |

| Selectividad                         | Pobre                                   | Muy bueno                                                        |  |

| Materiales removibles                | Sólo ciertos materiales                 | Todos                                                            |  |

| Escalabilidad del proceso            | Difícil                                 | Fácil                                                            |  |

| Limpieza del proceso                 | Condicionada                            | Muy bueno                                                        |  |

| Control dimensional crítico          | Muy bueno (<0.1µm)                      | Pobre                                                            |  |

| Costo de equipamiento                | Alto                                    | Relativamente bajo                                               |  |

| Velocidad típica de ataque           | Baja (0.1 – 0.6μm/min)                  | Rápido (>1µm/min)                                                |  |

| Parámetros operativos                | Muchos                                  | Pocos                                                            |  |

| Control sobre la velocidad de ataque | Bueno en caso de ataque lento           | Difícil                                                          |  |

Otra forma de clasificar a los procesos de micromaquinado es por su método de ataque o decapado, que puede ser húmedo o seco, es decir, eliminar material por medio de reacción química con soluciones líquidas o por procesos físicos en ambientes de gas y plasma respectivamente. Las comparativas entre los parámetros del proceso de decapado se presentan en la Tabla 1-8<sup>16</sup>.

El micromaquinado volumétrico tiene como propósito eliminar material del sustrato cristalino y puede aplicarse ya sea por la superficie superior (donde se depositan los otros materiales) con la intención de crear cavidades o por la cara inferior con el objetivo de crear membranas delgadas de silicio en la cercanía de la región activa, como se muestra en la Figura 1-15. El micromaquinado volumétrico suele ser un decapado húmedo con distintas soluciones reactivas que atacan a la red cristalina de silicio.

Esta cualidad cristalina del sustrato produce que el decapado sea anisotrópico en muchos de los casos, es decir, la velocidad de ataque varía según la orientación de la red, teniendo direcciones preferentes en las que el material se disuelve con mayor velocidad. En el presente trabajo así como en la mayoría de las aplicaciones académicas, se trabaja con sustratos de silicio cristalino tipo p, cuya superficie activa coincide con el plano (100) de la red. Los reactivos más comúnmente utilizados atacan al silicio y sus compuestos en la dirección preferencial con las velocidades mostradas en la Tabla 1-9<sup>17</sup>:

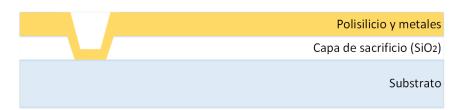

Los compuestos más utilizados como decapantes para el silicio y sus compuestos son el hidróxido de potasio (KOH), el etilendiamina y pirocaterol (EDP), el hidróxido de tetrametil amonio (TMAH) y la hidracina. Suelen utilizarse en solución 1:1 por peso con agua. En contraste, el micromaquinado superficial, procura mantener intacto al sustrato y genera microestructuras por encima de la superficie depositando materiales de la tecnología estándar apilados uno sobre otro, usualmente intercalados con capas conocidas como de sacrificio, las cuales generalmente son de óxido de silicio (SiO<sub>2</sub>). La capa de sacrificio provee un soporte mecánico inicial para generar las estructuras metálicas o semiconductoras deseadas. Después, mediante procedimientos fotolitográficos y de decapado, se elimina la capa de sacrificio liberando de esta forma la estructura del microsistema, generalmente en forma de membranas o vigas suspendidas por encima del sustrato, como se aprecia en la Figura 1-16. Para fines de

este trabajo se utilizará el micromaquinado superficial como método para liberar actuadores con características de membranas y resortes metálicos<sup>18</sup>.

#### 1.2. Aplicaciones y estado del arte

La tecnología MEMS surge como un derivado de la tecnología CMOS estándar, la cual predomina actualmente en la industria electrónica, sin embargo, es preciso remarcar que los avances particulares de la tecnología microelectromecánica han logrado tener hoy en día una industria plenamente dedicada a su desarrollo, excluyendo incluso algunos de los factores más representativos del proceso CMOS que los vio nacer.

Figura 1-15. Esquema de cavidades en el micromaquinado volumétrico.

| Tabla 1-9. | Velocidad d | e ataque | en el micror | naguinado | volumétrico |

|------------|-------------|----------|--------------|-----------|-------------|

|            |             |          |              |           |             |

| Material              | Decapante | Velocidad de ataque |  |

|-----------------------|-----------|---------------------|--|

| Silicio (100)         | КОН       | 0.25 – 1.4 μm/min   |  |

| Silicio (100)         | EDP       | 0.75 μm/min         |  |

| Óxido de silicio      | КОН       | 40 – 80 nm/h        |  |

|                       | EDP       | 12 nm/h             |  |

| Nitruro de silicio    | КОН       | 5 nm/h              |  |

| Twiti di o de silicio | EDP       | 6 nm/h              |  |

Figura 1-16. Esquema del micromaquinado superficial.

Más aún, en la actualidad los interruptores MEMS de tipo membrana se han desplegado a lo largo de la tecnología MOS de comunicaciones como un medio efectivo para el conmutado y control de señales de radiofrecuencia. Diversos dispositivos clasificados como RF-MEMS han sido descritos en la literatura principalmente por su desempeño en operación a altas frecuencias y su bajo consumo energético.

La gran mayoría de las aplicaciones de conmutación y filtrado de señales de radiofrecuencia basan su funcionamiento en el varactor electromecánico tipo shunt descrito en la sección 1.5 Elementos capacitivos del presente trabajo. Sin embargo, existen diversos desarrollos reportados en el que una línea de transmisión entra y sale del modo de conducción por medio de contacto mecánico como en el sistema aquí propuesto. De manera general, las características que respaldan el uso de interruptores microelectromecánicos de radiofrecuencia y suman a su viabilidad como dispositivo comercial son las siguientes<sup>19</sup>:

- Alta linealidad En comparación con los interruptores de estado sólido, los interruptores

MEMS convencionales han mostrado una linealidad hasta mil veces mayor.

- Alto aislamiento Por definición los interruptores electromecánicos tipo membrana consisten de una separación de aire entre los extremos de la línea de transmisión durante el estado off, esto garantiza una capacitancia parásita acoplada de muy pequeña y nulo flujo de corriente.

- Relativo bajo costo Costo comparable o menor a su versión macroscópica representada por los relevadores mecánicos, sin embargo, aún mucho mayor que su contraparte de estado sólido.

- Diseño simplificado En relación con los relevadores macroscópicos, el área de diseño requerida se reduce significativamente al no requerirse inductores ni polarización mediante un flujo de corriente directa.

- Bajo consumo de potencia Dada su naturaleza y estructura, de manera ideal los interruptores de actuación capacitiva no consumen corriente y, a pesar de los altos potenciales de actuación y circuitería requeridos su consumo es menor que el de los interruptores tipo diodo.

Cabe resaltar también las desventajas más significativas de los interruptores microelectromecánicos, las cuales se presentan principalmente en comparación con sus equivalentes de estado sólido:

- Baja velocidad de conmutación Por su naturaleza mecánica la frecuencia máxima de operación es muchas veces menor que aquella para los transistores e interruptores de estado sólido.

- Baja confiabilidad Si bien el desarrollo continúa y la confiabilidad va en ascenso día con día, los interruptores con elementos micromecánicos tienden a fallar en una mucho mayor proporción que sus similares de funcionamiento totalmente electrónico.

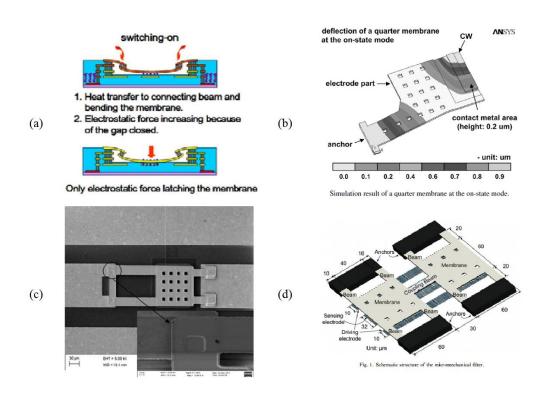

En *Design of Multi-actuation RF MEMS Switch Using CMOS Process* (Lee, Ko, & Huang, 2008) se muestra un interruptor RF MEMS capacitivo actuado por fuerza electrotérmica y electrostática de manera simultánea. Una vez obtenido el desplazamiento deseado, el sostenimiento del mismo se realiza únicamente por fuerza de atracción electrostática utilizando un voltaje y consumo de potencia relativamente bajos.

El dispositivo mostrado en la Figura 1-17 (a) fue fabricado en la tecnología CMOS estándar 2P4M de  $0.35\mu m$  y se le aplicó un post-proceso para la liberación de la estructura que consiste de una guía de onda coplanar (CPW) y una membrana sujeta por elementos de resorte en la capa de Metal 4.

Figura 1-17. Reportes de la literatura en RF-MEMS.

En este esquema se obtiene ventaja de la expansión térmica que por efecto Joule se presenta en la membrana para dar un impulso inicial al desplazamiento. Por su parte, en el artículo A Low-Loss Single-Pole Six-Throw Switch Based on Compact RF MEMS Switches (Lee, Je, Kang, & Choi, 2005) introducen un multi-interruptor de un polo y seis tiros de contacto metálico implementado en un área menor a 1mm<sup>2</sup> y con parámetros de aislamiento e inserción del orden de -30.6dB y -0.1dB respectivamente, en operación hasta 20GHz. La Figura 1-17 (b) muestra una simulación multifísica simétrica de la membrana y su elemento de resorte asociado. Contribuyendo al estudio de los RF-MEMS como elementos de conmutación, Fabrication and characterization of RF MEMS high isolation switch up to Xband (Dey, Parihar, & Koul, 2013) presenta avances recientes en el desarrollo de un microactuador acoplado a una CPW y alcanzando de manera experimental una característica de aislamiento del orden de -60dB en frecuencias de hasta 12GHz. Una microfotografía SEM del actuador en cantiléver se presenta en la Figura 1-17 (c). Más allá de los microinterruptores de guías de onda coplanar, una manera de aislar señales de alta frecuencia es por medio de filtros como el presentado en Simulation and fabrication of HF microelectromechanical bandpass filter (Dai, Chiang, & Chang, 2007) donde la Universidad Nacional Chung Hsing y el Centro de Tecnología RFID de Taiwan exponen el microfiltro pasabanda de la Figura 1-17 (d) fabricado en dimensiones del orden de  $150\mu m$  dentro de la tecnología CMOS estándar de 0.35µm y de probada eficiencia en una señal base de 39.6MHz, la cual puede ser aprovechada en aplicaciones de radiofrecuencia comunes.

Cabe señalar que los desarrollos aquí citados, así como la gran mayoría de las aplicaciones industriales suman esfuerzos en el control, modulación y transmisión de señales de radiofrecuencia, todas ellas en frecuencias comerciales y de alta velocidad de transferencia de datos, sin embargo, el presente trabajo busca implementar la arquitectura RF-MEMS en las tareas de control, carga y descarga del potencial eléctrico de la compuerta flotante de un transistor FGMOS, elaborando diseños y simulaciones físicas dentro del marco de la tecnología CMOS estándar de 0.5µm y combinando las experiencias previas del grupo de investigación como los son Sensor Inteligente de Imágenes en Tecnología CMOS, con Aplicaciones en Robótica (Ponce-Ponce, 2005) y Red Neuronal Celular Programable en Tecnología CMOS (Molinar-Solis, 2006) con algoritmos de control probados para el

sostenimiento del potencial flotante como lo es *Clock-Controlled Neuron-MOS Logic Gates* (Kotani, Shibata, Imai, & Ohmi, 1998) donde un esquema de sincronía refresca de manera periódica la carga presente en la compuerta flotante y permite a sistemas de funcionamiento cuasi-flotante desarrollar tareas de almacenamiento no volátil.

#### 1.3. MEMS electrostáticos

La gran mayoría de los MEMS en uso comercial pueden clasificarse por el tipo de energía que se intercambia para obtener la señal de información, es decir, el tipo de fuerza que se ejerce hacia o desde el sensor o actuador principal:

- Fuerzas Electrostáticas,

- Fuerzas Magnéticas,

- Fuerzas Térmicas y

- Fuerzas Piezoeléctricas.

En el mercado y la industria dominan principalmente los MEMS de fuerzas electrostática y electrotérmica y se hacen presentes en una amplia variedad de aplicaciones. Por otra parte los MEMS de principios piezoeléctricos, si bien son utilizados de manera masiva, sus aplicaciones son relativamente pocas y bastante específicas. Por último, los MEMS de propiedades magnéticas, son por el momento objeto de estudio más que de aplicación práctica, debido a su dificultad en la fabricación de bobinas y elementos magnetostáticos en la tecnología planar actual de fabricación de semiconductores.

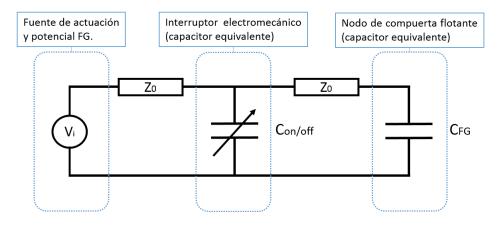

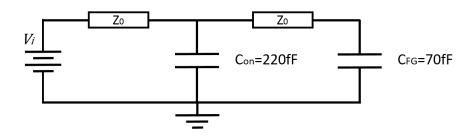

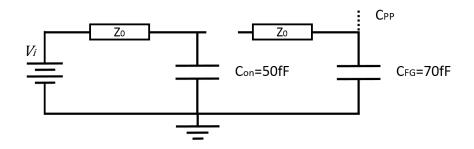

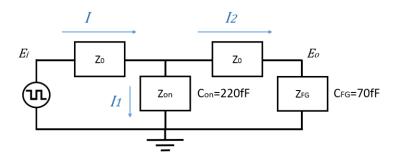

Es de nuestro interés analizar las características de consumo de energía, potencia, eficiencia mecánico-eléctrica y optimización de los microsistemas electrostáticos, para lo que es fundamental conocer cómo las magnitudes físicas y fenómenos que afectan al mundo macroscópico, se modifican en función del tamaño de los sujetos de prueba, en este caso, para dimensiones y cuerpos masivos micrométricos. En general, la física tiene un comportamiento distinto a micro-escala y los dispositivos y sistemas microelectromecánicos deben basarse en principios de operación diferentes a los de su contraparte macroscópica.