## Centro de Investigación y de Estudios Avanzados del Instituto Politécnico Nacional Unidad Zacatenco

# Caracterización de las propiedades funcionales de un acelerómetro CMOS-MEMS basado en el FGMOS

Tesis que presenta

## Benito Granados Rojas

para obtener el grado de

Doctor en Ciencias

en la especialidad de Ingeniería Eléctrica

Director de Tesis: Dr. Mario Alfredo Reyes Barranca

Ciudad de México 2021

# Agradecimientos

Agradezco a mi familia, compañeros y profesores por ser fuente de motivación e inspiración para la culminación de esta etapa. Mi hija Emma y mi esposa Yesenia son las estrellas que guían mi camino. Mis padres, Doña Carmen Rojas y Don Antonio Granados, fortalecen mis pasos.

Expreso mi gratitud absoluta al Dr. Mario Alfredo Reyes Barranca, una persona a quien estimo como a un amigo y a quien debo la consecución de este objetivo tan importante en mi vida. Agradezco igualmente a los revisores de este trabajo, Dr. Felipe Gómez, Dr. Gabriel Romero, Dr. Yasuhiro Matsumoto y Dr. Salvador Mendoza, ya que sus oportunas observaciones enriquecieron enormemente el resultado final del presente proyecto.

Mi gratitud se extiende también al personal académico del Laboratorio de Sistemas VLSI, especialmente al M. en C. Luis Martín Flores, una persona que contagia su entusiasmo por aprender y que junto con el Dr. Oliverio Arellano y el M. en I. Emilio Rafael Espinosa tuvieron siempre un momento para compartir conocimientos y discutir ideas. Agradezco también a la Coordinación Acádemica de la Sección de Electrónica del Estado Sólido, cuyos integrantes a través de los años cobijaron mi crecimiento profesional.

Me permito también agradecer y felicitar a mis compañeros de clase, que se convirtieron en mis amigos, colegas y compañeros de aventuras. Desde el primer día el Cinvestav me hizo sentir como en casa y la SEES se convirtió rápidamente en una familia. No menos importante es reconocer la labor del **Conacyt**, cuyos recursos y gestión hicieron posible este sueño cumplido.

A todos, muchas gracias

# Contenido

|   | Índi  | ce de figuras                                           | j    |

|---|-------|---------------------------------------------------------|------|

|   | Índio | ce de tablas                                            | vii  |

|   | Resu  | ımen                                                    | ix   |

|   | Abst  | ract                                                    | X    |

|   | Obje  | etivos                                                  | xiii |

|   |       |                                                         |      |

| 1 | Intr  | oducción                                                | 1    |

|   | 1.1   | Antecedentes                                            | 2    |

|   |       | 1.1.1 Tecnología CMOS convencional                      | 4    |

|   |       |                                                         | 7    |

|   |       | 1.1.3 FGMOS                                             | 12   |

|   |       | 1.1.4 Metaheurísticas bio-inspiradas                    | 12   |

|   |       | 1.1.5 Algoritmos genéticos                              | 14   |

|   | 1.2   | Estado del arte                                         | 18   |

|   |       | 1.2.1 Dispositivos comerciales y proyectos académicos   | 18   |

|   |       | 1.2.2 Uso de algoritmos genéticos en el diseño de cir-  |      |

|   |       | cuitos integrados                                       | 20   |

|   | 1.3   | Conclusiones del capítulo                               | 21   |

| 2 | Asp   | ectos teóricos                                          | 23   |

|   | 2.1   | Acelerometría                                           | 23   |

|   | 2.2   | Sensitividad                                            | 24   |

|   | 2.3   | Sistema masa-resorte                                    | 26   |

|   | 2.4   | Modelo dinámico                                         | 30   |

|   |       | 2.4.1 Respuesta al escalón y respuesta a entrada lineal | 32   |

|   |       | 2.4.2 Respuesta amortiguada                             | 36   |

|   | 2.5   | El EGMOS en términos de su geometría                    | 38   |

### **CONTENIDO**

|    | 2.6   | Dos objetivos en conflicto                             |

|----|-------|--------------------------------------------------------|

|    | 2.7   | Conclusiones del capítulo                              |

| 3  | Asp   | ectos tecnológicos 53                                  |

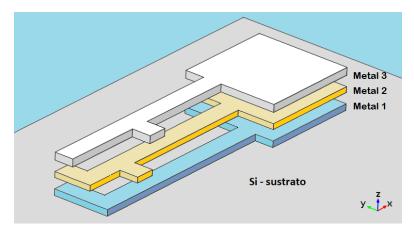

|    | 3.1   | Composición de las capas metálicas 53                  |

|    | 3.2   | Micro-maquinado superficial 63                         |

|    | 3.3   | Conclusiones del capítulo 67                           |

| 4  | Dise  | eño CMOS-MEMS 69                                       |

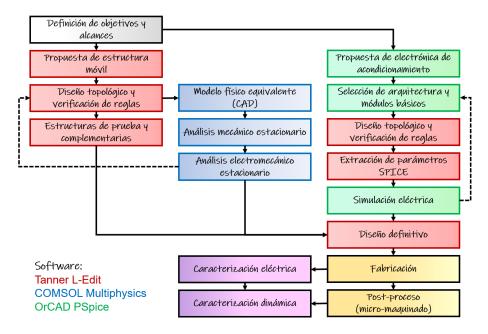

|    | 4.1   | Metodología de diseño                                  |

|    | 4.2   | Estructura capacitiva tridimensional                   |

|    |       | 4.2.1 Simulación multi-física 81                       |

|    |       | 4.2.2 Efectos gravitacionales sobre la masa sísmica 82 |

|    | 4.3   | Simulación y validación eléctrica                      |

|    |       | 4.3.1 Acondicionamiento de señal 87                    |

|    |       | 4.3.2 Validación eléctrica 96                          |

|    | 4.4   | CAD y layout                                           |

|    | 4.5   | Conclusiones del capítulo                              |

| 5  | Dise  | eño metaheurístico 109                                 |

|    | 5.1   | Optimización mono-objetivo                             |

|    | 5.2   | Optimización multi-objetivo                            |

|    |       | 5.2.1 Codificación de variables                        |

|    |       | 5.2.2 Metaheurística bio-inspirada                     |

|    | 5.3   | Resultados y simulación adicional                      |

|    | 5.4   | Conclusiones del capítulo                              |

| 6  | Con   | clusiones generales 135                                |

|    | 6.1   | Resultados y aportaciones                              |

|    | 6.2   | Productos y publicaciones                              |

|    | 6.3   | Trabajo futuro                                         |

| Aı | iexos | 141                                                    |

|    | Ane   | xo A: Parámetros tecnológicos                          |

|    |       | xo B: Código Matlab Livescript                         |

|    |       | xo C: Estructuras complementarias                      |

# Índice de figuras

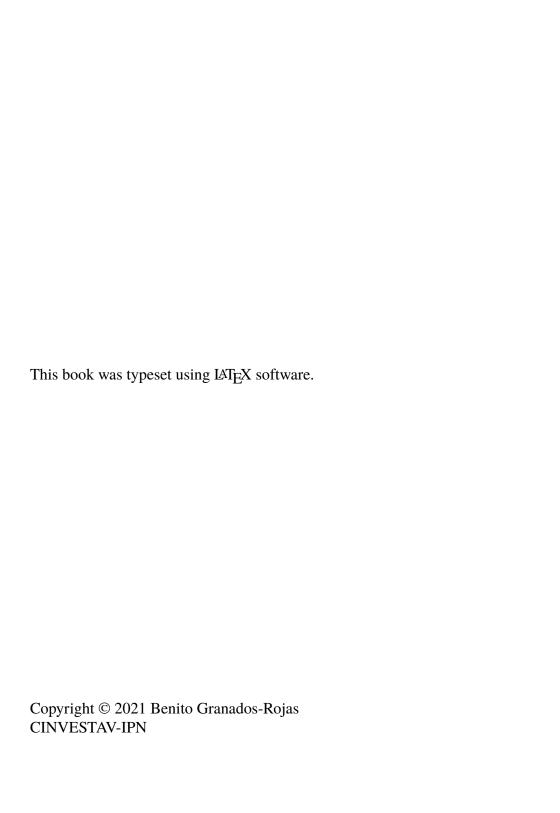

| 1.1  | Resumen del proceso de obtención de obleas de silicio   |    |

|------|---------------------------------------------------------|----|

|      | cristalino                                              | 4  |

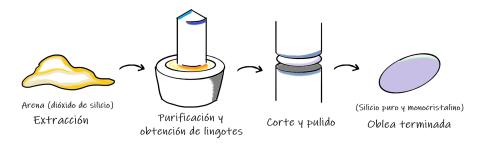

| 1.2  | Terminales del transistor MOSFET canal P y canal N, y   |    |

|      | proceso de formación del canal                          | 5  |

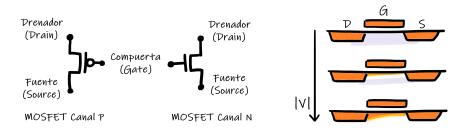

| 1.3  | Transistores MOS complementarios en un mismo sustrato.  | 6  |

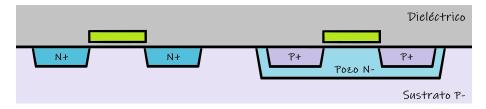

| 1.4  | Capas disponibles en el proceso de fabricación C5 de    |    |

|      | ON Semiconductor                                        | 7  |

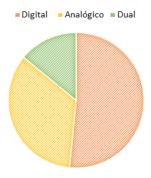

| 1.5  | Clasificación del acelerómetro capacitivo               | 8  |

| 1.6  | Acelerómetro capacitivo y sistema masa-resorte equiva-  |    |

|      | lente                                                   | 8  |

| 1.7  | Alambrado externo entre dados independientes            | 9  |

| 1.8  | Integración monolítica CMOS-MEMS                        | 10 |

| 1.9  | Liberación de un resorte metálico                       | 11 |

| 1.10 | Transistor de compuerta flotante                        | 12 |

| 1.11 | Resumen de algoritmos naturalmente inspirados más co-   |    |

|      | munes                                                   | 14 |

| 1.12 | Cromosoma incluyendo todas las variables codificadas    |    |

|      | en una misma cadena binaria                             | 16 |

| 1.13 | Ubicación de los frentes de Pareto y los puntos óptimos |    |

|      | ideales (utópicos)                                      | 17 |

| 1.14 | Distribución de mercado de acelerómetros comerciales    | 19 |

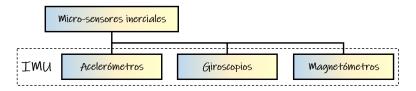

| 2.1  | Unidad de medición inercial                             | 24 |

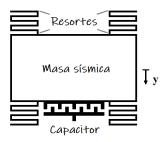

| 2.2  | Esquemático de una estructura típica basada en un sis-  |    |

|      | 1                                                       | 27 |

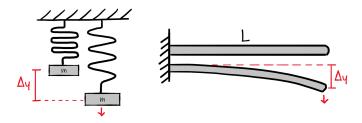

| 2.3  | _                                                       | 29 |

|      | 1                                                       |    |

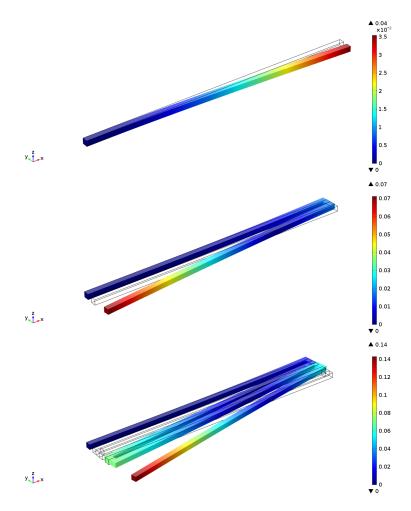

| 2.4  | validación por FEA del comportamiento de un resorte conformado por n vigas individuales. Desplazamiento proporcional del extremo libre ante una misma fuerza |    |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | para un número de vigas $n = 1, 2 y 4 \dots \dots$                                                                                                           | 31 |

| 2.5  | Diagrama de cuerpo libre correspondiente a una masa m                                                                                                        |    |

|      | y un único resorte con rigidez total equivalente k                                                                                                           | 31 |

| 2.6  | Representación en lazo abierto del sistema masa-resorte.                                                                                                     | 32 |

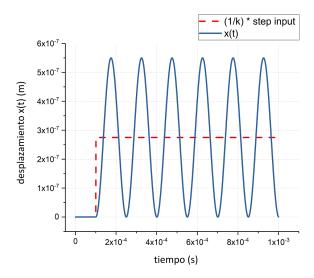

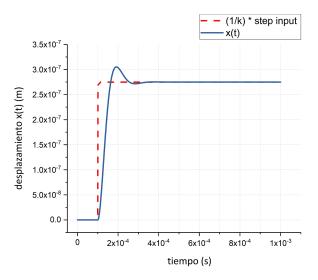

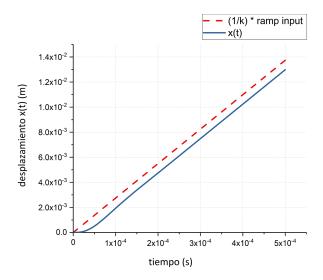

| 2.7  | Respuesta oscilatoria ante un escalón unitario en condi-                                                                                                     |    |

|      | ciones libres de gravedad y amortiguamiento por aire                                                                                                         | 35 |

| 2.8  | Error sinusoidal ante una rampa en condiciones libres de                                                                                                     |    |

|      | gravedad y amortiguamiento por aire                                                                                                                          | 35 |

| 2.9  | Estados transitorio y estable de un acelerómetro con amor-                                                                                                   |    |

|      | tiguamiento ante una entrada de tipo escalón                                                                                                                 | 37 |

| 2.10 | Respuesta amortiguada usual ante una entrada lineal, pre-                                                                                                    |    |

|      | sentando error en estado estacionario                                                                                                                        | 38 |

| 2.11 | Divisor de voltaje capacitivo equivalente                                                                                                                    | 40 |

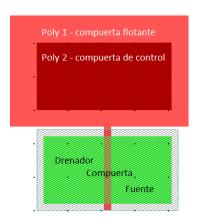

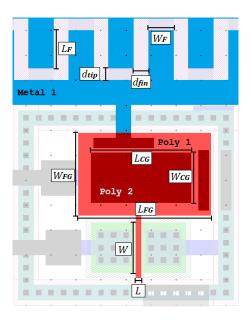

| 2.12 | Bosquejo de layout para un transistor de compuerta flotante                                                                                                  |    |

|      | (CAD)                                                                                                                                                        | 41 |

| 2.13 | Capas del capacitor poly-a-poly (por encima del óxido                                                                                                        |    |

|      | de campo)                                                                                                                                                    | 42 |

| 2.14 | Esquema simplificado del sensor inercial basado en FG-                                                                                                       |    |

|      | MOS                                                                                                                                                          | 43 |

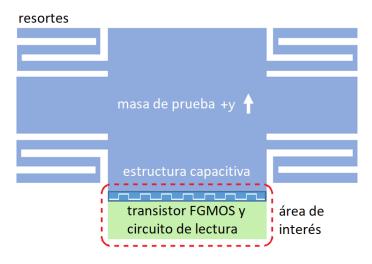

| 2.15 | Componentes del sensor inercial basado en FGMOS)                                                                                                             | 44 |

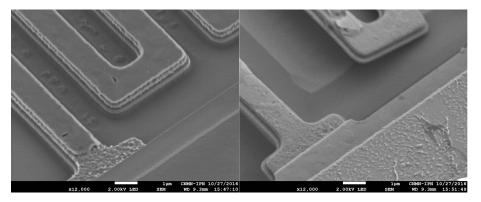

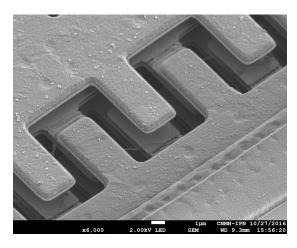

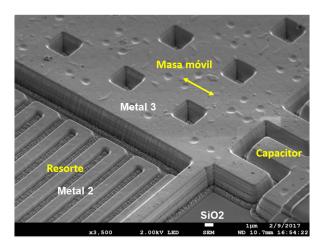

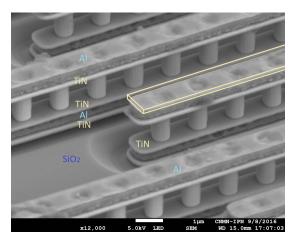

| 2.16 | Micrografía SEM de la estructura CMOS-MEMS                                                                                                                   | 45 |

| 2.17 | Sistema masa-resorte con cuatro resortes y una estruc-                                                                                                       |    |

|      | tura capacitiva.                                                                                                                                             | 47 |

| 2.18 | Variables topológicas en el FGMOS y en la estructura                                                                                                         |    |

|      | capacitiva MEMS multicapa                                                                                                                                    | 51 |

| 3.1  | Distribución de las tres capas metálicas del proceso de                                                                                                      |    |

| 3.1  | $0.5\mu \text{m}$ de On Semi                                                                                                                                 | 54 |

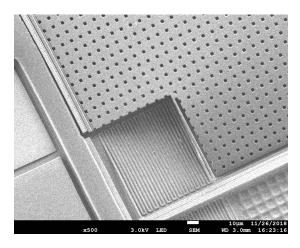

| 3.2  | Pads y ventanas de Overglass.                                                                                                                                | 56 |

| 3.3  | Estructuras en metal 2 y 3 a través de una ventana de                                                                                                        |    |

|      | Overglass                                                                                                                                                    | 57 |

| 3.4  | Todas las capas del proceso C5 tras haber realizado el                                                                                                       | ٠, |

|      | micro-maquinado químico                                                                                                                                      | 58 |

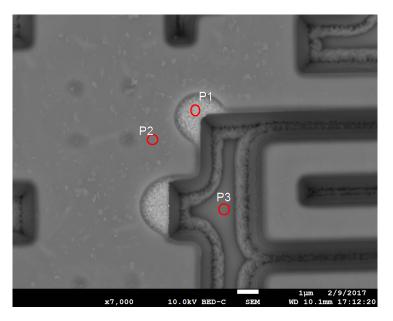

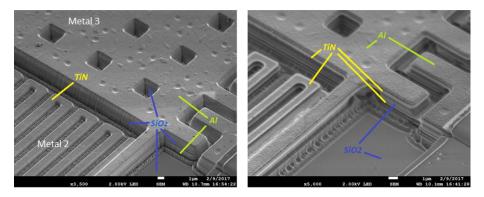

| 3.5  | Micro-fotografía de muestras de materiales                                                                                                                   | 58 |

| 3.6  | Puntos objetivo del análisis EDS                                      | 59       |

|------|-----------------------------------------------------------------------|----------|

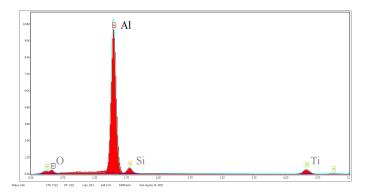

| 3.7  | Espectro EDS del punto P1 mostrando presencia de Alu-                 |          |

|      | minio                                                                 | 60       |

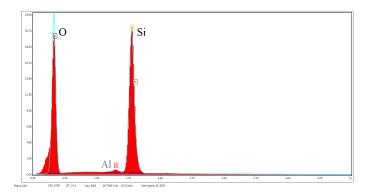

| 3.8  | Espectro EDS del punto P3 mostrando presencia de oxígeno y silicio    | 60       |

| 3.9  | •                                                                     |          |

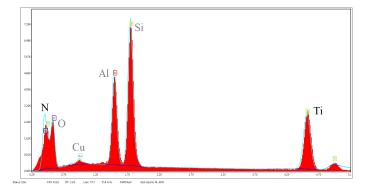

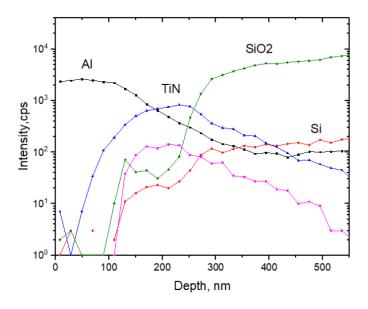

| 3.9  | Espectro EDS del punto P2 mostrando presencia de nitrógene            |          |

| 3.10 | y titanio                                                             | 60<br>61 |

|      | Estructura metálica degradada tras post-proceso de mi-                | 01       |

| 5.11 | cromaquinado.                                                         | 62       |

| 3.12 | Daño estructural debido a tensiones superficiales                     | 63       |

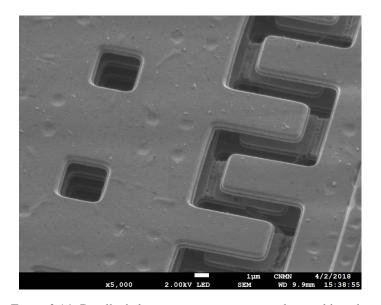

| 3.13 | Resultado de un ataque parcial (incompleto debido a una               |          |

|      | breve exposición)                                                     | 66       |

| 3.14 | Detalle de la estructura capacitiva totalmente liberada               | 66       |

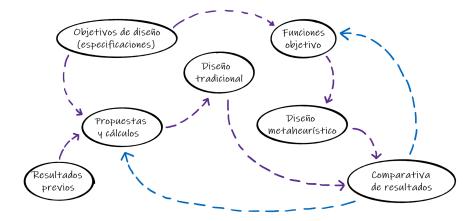

| 4.1  | Metodología de diseño                                                 | 71       |

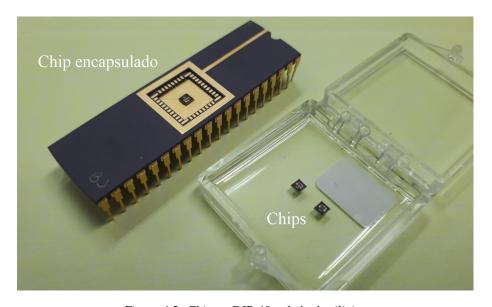

| 4.2  | Chip en DIP-40 y dado de silicio                                      | 72       |

| 4.3  | Parámetros geométricos del capacitor de placas paralelas.             | 74       |

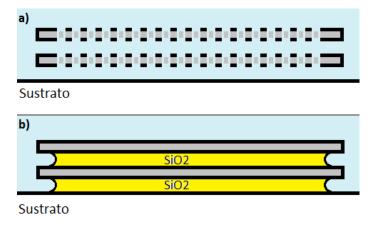

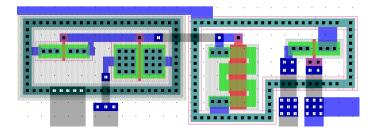

| 4.4  | (a) estructura perforada y totalmente liberada (b) estruc-            |          |

|      | tura de placa sólida (con restos de dióxido de silicio in-            |          |

|      | accesibles)                                                           | 75       |

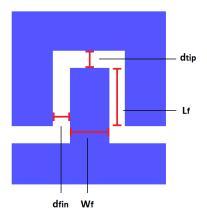

| 4.5  | Parámetros geométricos de un dedo metálico                            | 76       |

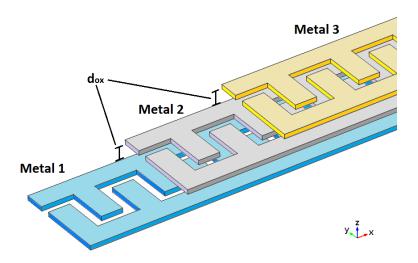

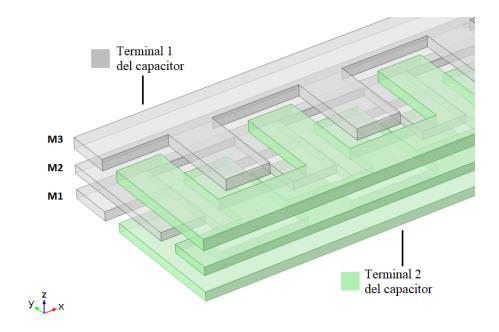

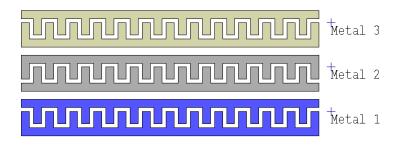

| 4.6  | Arreglo inter-digitado en las diferentes capas metálicas              |          |

|      | disponibles. Los dedos de Metal 2 se traslapan parcial-               |          |

|      | mente sobre los dedos de Metal 1, de igual manera los                 | 77       |

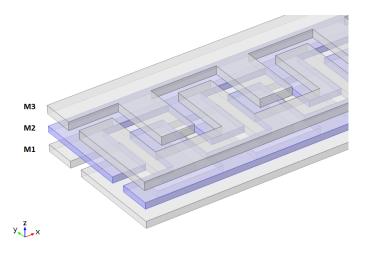

| 4.7  | dedos de Metal 3 se traslapan sobre los dedos de Metal 2.             | 77       |

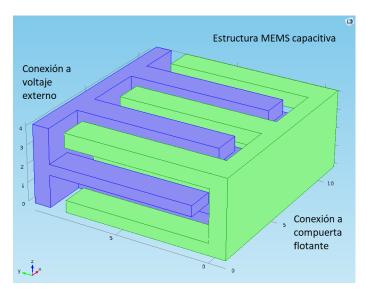

| 4.7  | Renderizado 3D de la estructura capacitiva                            | 78       |

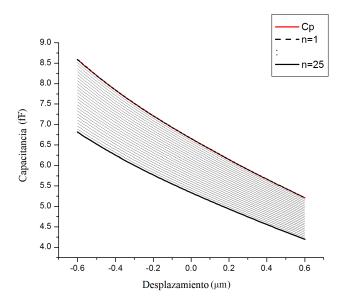

| 4.8  | Capacitancia para estructuras inter-digitadas desde 1 hasta 25 dedos. | 79       |

| 4.9  |                                                                       | 80       |

| 4.9  | Comparativa de arquitecturas capacitivas                              | 00       |

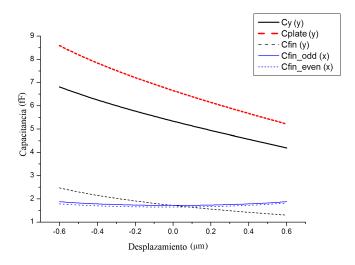

| 4.10 | desplazamiento                                                        | 81       |

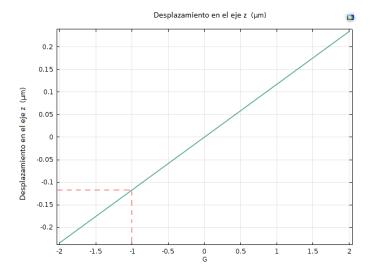

| 4.11 | Desplazamiento prescrito en el eje z debido a una acel-               | 01       |

|      | eración de 1 g en dirección hacia abajo                               | 82       |

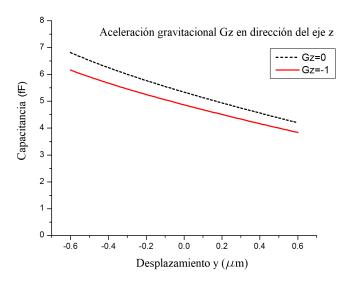

| 4.12 | Capacitancia total considerando y descartando los efec-               |          |

|      | tos gravitacionales                                                   | 83       |

| 4.13 | Arquitectura del FGMOS y su equivalente capacitivo                    | 85       |

|      |                                                                       |          |

| 4.14 | Equivalente capacitivo del dispositivo con multiples com-  |     |

|------|------------------------------------------------------------|-----|

|      | puertas de control                                         | 86  |

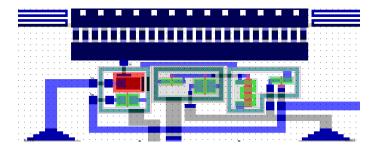

| 4.15 | Circuito de lectura de dos etapas                          | 88  |

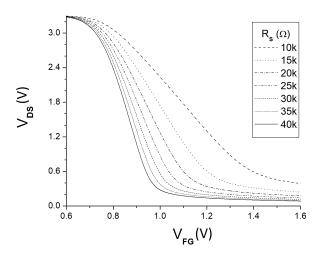

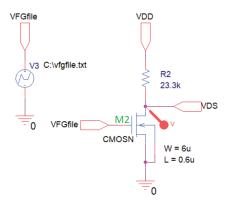

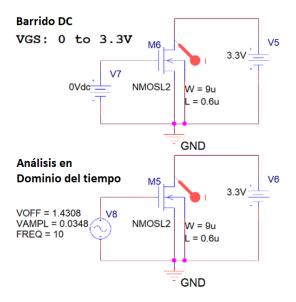

| 4.16 | Arreglo para simulación de la primera etapa                | 89  |

| 4.17 | Barrido de resistencia R en búsqueda de una polarización   |     |

|      | conveniente para el nodo de drenador                       | 90  |

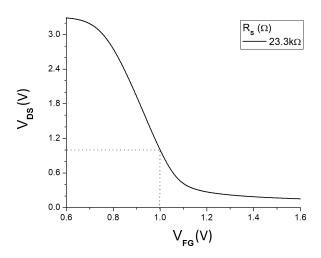

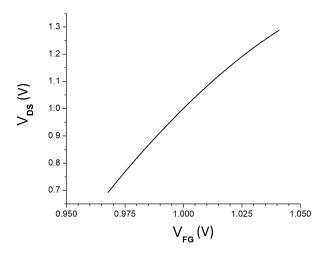

| 4.18 | Punto de operación seleccionado para la característica     |     |

|      | drenador-fuente                                            | 90  |

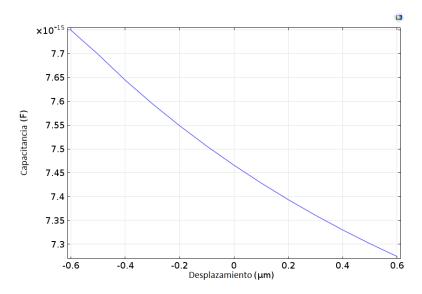

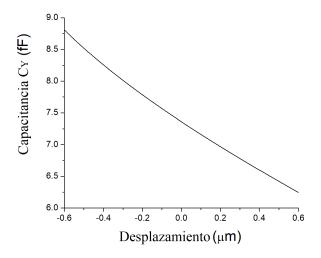

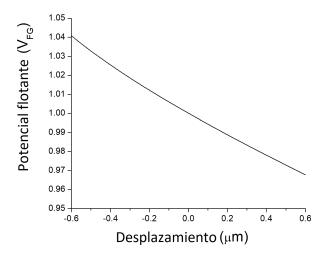

| 4.19 | Variaciones de capacitancia de acuerdo con el desplaza-    |     |

|      | miento                                                     | 91  |

| 4.20 | Potencial flotante de acuerdo con el desplazamiento        | 91  |

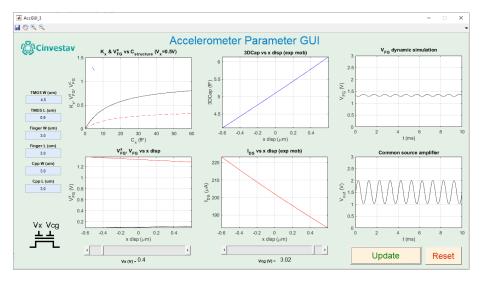

| 4.21 | Interfaz gráfica auxiliar en la selección de parámetros    | 92  |

| 4.22 | Esquemático de simulación con entrada no lineal previ-     |     |

|      | amente computada                                           | 93  |

| 4.23 | Voltaje drenador-fuente como salida en función del po-     |     |

|      | tencial flotante                                           | 94  |

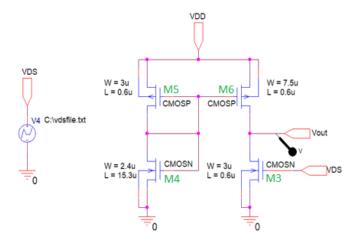

| 4.24 | Configuración de simulación para la segunda etapa          | 95  |

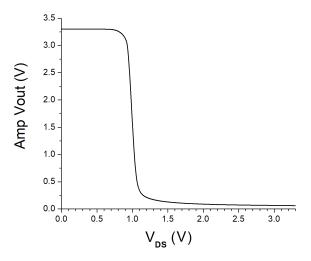

| 4.25 | Simulación de la característica del amplificador de fuente |     |

|      | común                                                      | 96  |

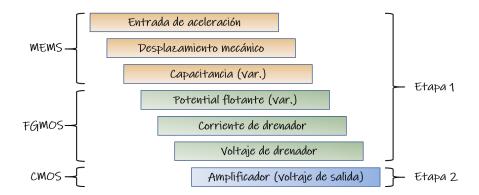

| 4.26 | Flujo de señales                                           | 97  |

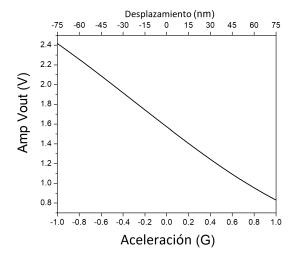

| 4.27 | Característica voltaje vs acceleración                     | 97  |

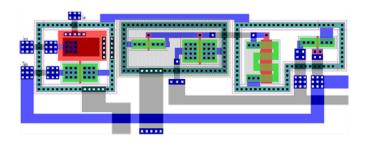

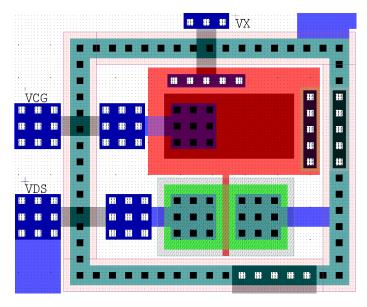

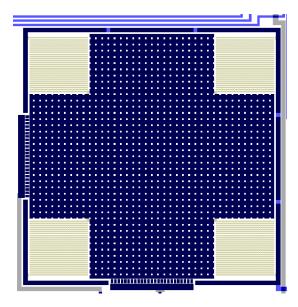

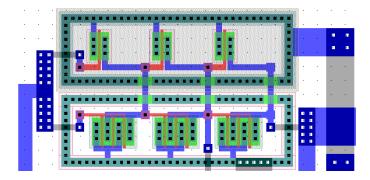

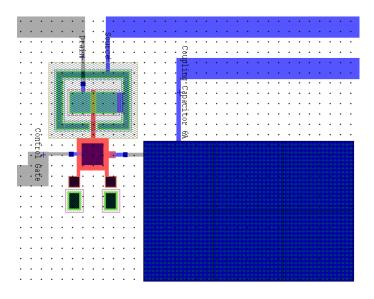

| 4.28 | Layout del FGMOS y el amplificador de fuente común         | 99  |

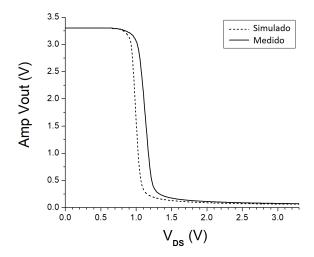

| 4.29 | Características de simulación y medición                   | 99  |

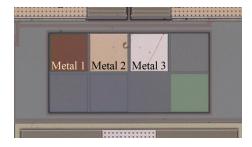

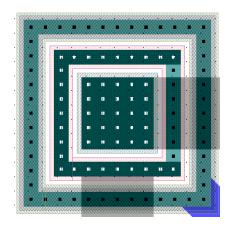

| 4.30 | Capas de la estructura capacitiva variable                 | 101 |

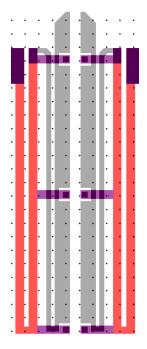

| 4.31 | Layout de cada una de las capas metálicas en la estruc-    |     |

|      | tura capacitiva                                            | 101 |

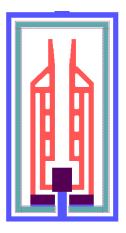

| 4.32 | Layout del transistor de compuera flotante                 | 103 |

| 4.33 | Layout del amplificador de fuente común                    | 103 |

| 4.34 | Layout de la región que incluye al FGMOS, el amplifi-      |     |

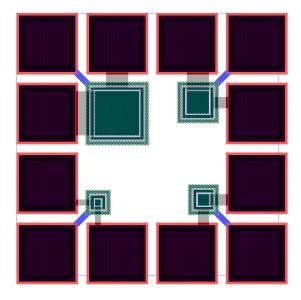

|      | cador y la estructura capacitiva                           | 103 |

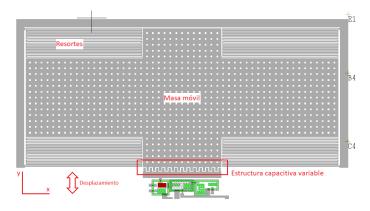

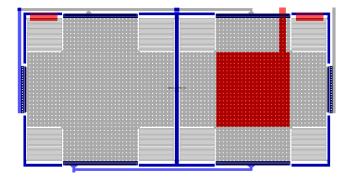

|      | Layout del acelerómetro principal                          |     |

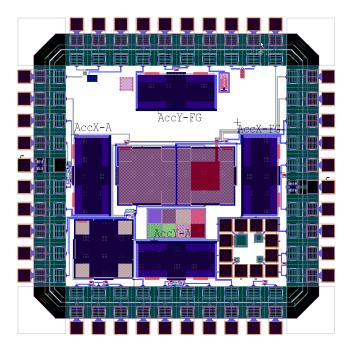

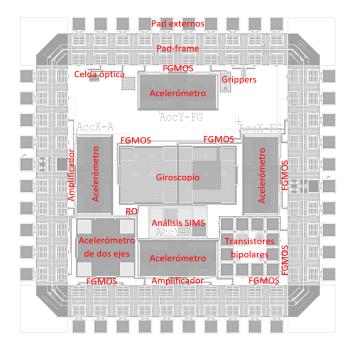

|      | Layout del chip completo                                   |     |

| 4.37 | Diversas estructuras de prueba incluidas en el proyecto    | 105 |

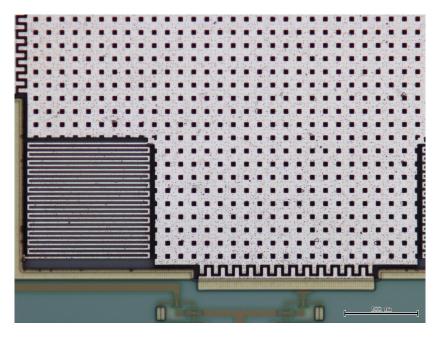

|      | Micrografía óptica del chip fabricado                      | 106 |

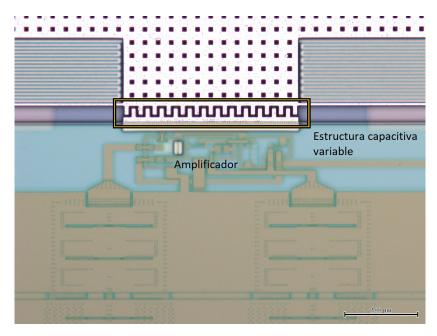

| 4.39 | Micrografía óptica de la región que incluye al FGMOS,      |     |

|      | el amplificador y la estructura capacitiva                 | 107 |

| 4.40 | Detalle de los resortes en un acelerómetro de dos ejes     | 107 |

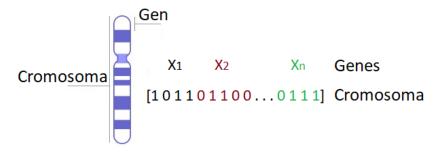

| 5.1  | Interpretación del gen y el cromosoma                                        | 112 |

|------|------------------------------------------------------------------------------|-----|

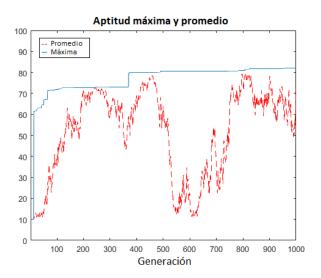

| 5.2  | Población: 100, P <sub>C</sub> : 0.7, P <sub>M</sub> : 0.01, aptitud máxima: |     |

|      | 82.22, aptitud media con grandes variaciones a través                        |     |

|      | de las generaciones                                                          | 115 |

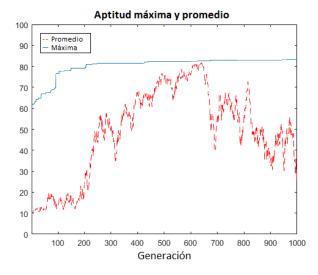

| 5.3  | Población: 200, P <sub>C</sub> : 0.7, P <sub>M</sub> : 0.01, aptitud máxima: |     |

|      | 83.19, la aptitud media se establece en un rango medio                       |     |

|      | indicando mayor diversidad entre los individuos de la                        |     |

|      | 1                                                                            | 115 |

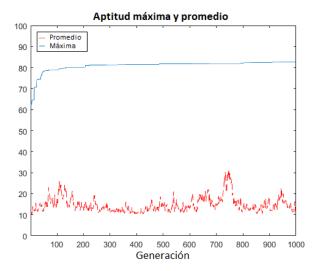

| 5.4  | Población: 200, P <sub>C</sub> : 0.8, P <sub>M</sub> : 0.05, aptitud máxima: |     |

|      | 82.71. Con tasas altas de mutación aparecen problemas                        |     |

|      | de convergencia rápida, aún cuando la aptitud media per-                     |     |

|      | manece baja, esto resulta crítico cuando se tiene un es-                     |     |

|      | pacio de búsqueda con múltiples óptimos locales                              |     |

| 5.5  | Aproximación al espacio de búsqueda                                          | 120 |

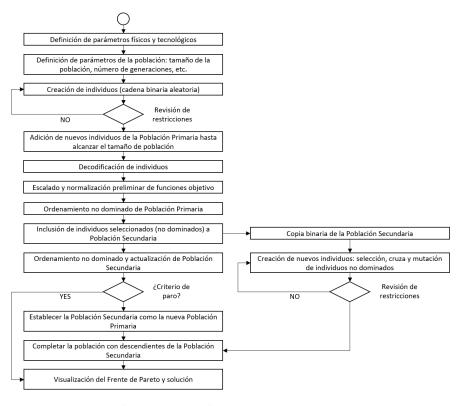

| 5.6  | Diagrama de flujo del algoritmo multi-objetivo                               | 122 |

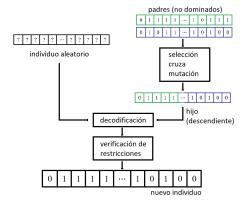

| 5.7  | Creación de nuevos individuos                                                | 122 |

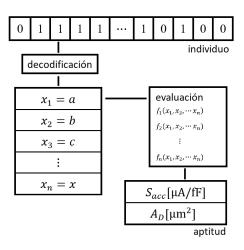

| 5.8  | Decodificación y evaluación de nuevos individuos                             | 123 |

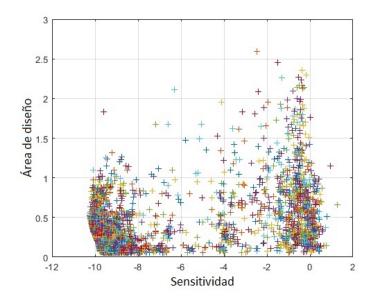

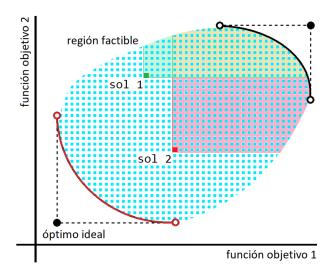

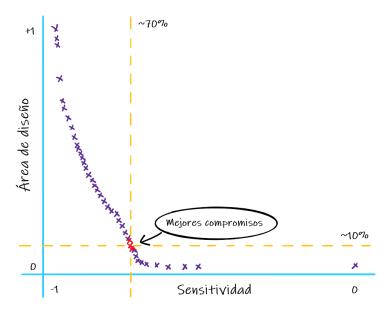

| 5.9  | Conjunto de soluciones no-dominadas                                          | 124 |

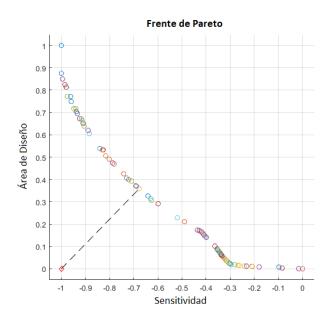

| 5.10 | Solución más cercana al óptimo ideal                                         | 125 |

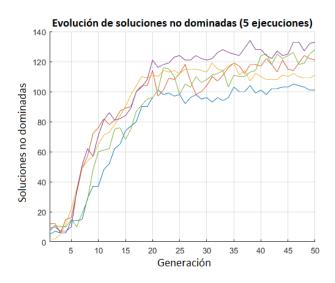

| 5.11 | Evolución del número de soluciones no dominadas                              | 127 |

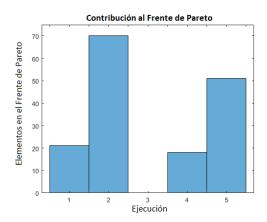

| 5.12 | Contribución de cada ejecución en el Frente de Pareto                        |     |

|      | final de acuerdo al número de soluciones no dominadas                        | 128 |

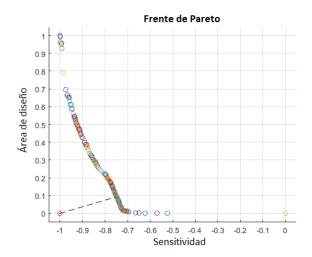

| 5.13 | Frente de Pareto definitivo en el análisis                                   | 129 |

| 5.14 | Modelo CAD de la estructura capacitiva interdigital                          | 131 |

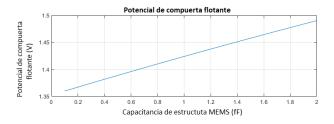

| 5.15 | Potencial flotante de acuerdo con la capacitancia de la                      |     |

|      | estructura MEMS                                                              | 131 |

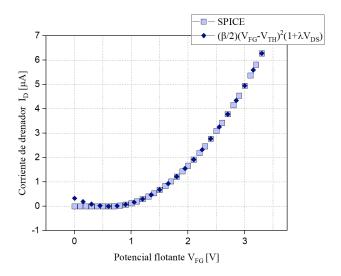

| 5.16 | Coincidencia entre la simulación SPICE y la corriente                        |     |

|      | de drenador calculada evaluando el modelo sujeto a op-                       |     |

|      | timización                                                                   | 132 |

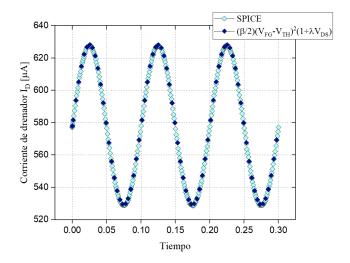

| 5.17 | Aproximación a la respuesta a una entrada oscilatoria                        |     |

|      | dentro del rango de desplazamiento de la estructura ca-                      |     |

|      | pacitiva                                                                     | 133 |

| 5.18 | Configuración y conexión del FGMOS utilizado para sim-                       |     |

|      | ulación SPICE                                                                | 133 |

| 6.1  | Esquema del proceso realizado                                                | 136 |

|      | Desempeño cualitativo.                                                       |     |

| 6.3  | Layout de una variante de acelerómetro                   |

|------|----------------------------------------------------------|

| 6.4  | Layout de un prototipo de giroscopio                     |

| 6.5  | Gripper actuado electrostáticamente                      |

| 6.6  | Gripper actuado por dilatación térmica 149               |

| 6.7  | Prototipo de oscilador de anillo                         |

| 6.8  | Prototipo de foto-diodo basado en FGMOS 150              |

| 6.9  | Celda de prueba de transistores bipolares (fabricados en |

|      | tecnología CMOS)                                         |

| 6.10 | Detalle de un transistor bipolar                         |

# Índice de tablas

| 1.1 | Resumen de trabajos académicos basados en acelerómetros     |

|-----|-------------------------------------------------------------|

|     | MEMS y CMOS-MEMS                                            |

| 3.1 | Parámetros estructurales                                    |

| 3.2 | Subestructuras metálicas                                    |

| 5.1 | Parámetros de diseño                                        |

| 5.2 | Codificación de variables (optimización mono-objetivo). 114 |

| 5.3 | Parámetros computados (resultado final)                     |

| 5.4 | Rango y codificación de variables (optimización multi-      |

|     | objetivo)                                                   |

| 5.5 | Resumen de resultados                                       |

| 5.6 | Resumen de resultados en ordenamiento final 128             |

| 5.7 | Topología de la solución final                              |

## Resumen

En el presente trabajo se busca establecer un procedimiento para automatizar parte del proceso de diseño de un acelerómetro capacitivo por medio de la implementación de un algoritmo metaheurístico bio-inspirado y partiendo de un análisis de los parámetros que modelan el desempeño de un sensor inercial. Dicho sensor está pensado para cumplir con las especificaciones y normas de diseño que permitan su fabricación bajo el proceso CMOS estándar de  $0.5\mu m$ , lo que da lugar a un dispositivo micro-electromecánico integrado y monolítico del tipo conocido como CMOS-MEMS. A lo largo del trabajo de investigación se aborda principalmente el caso de un micro-sensor inercial cuyo principio de transducción se basa en los cambios de capacitancia y potencial eléctrico propios de un transistor MOS de compuerta flotante (FGMOS), sin embargo, se hace destacar que los procedimientos y técnicas propuestos a lo largo del documento tienen un espectro de aplicación factible sobre una variedad de sensores y actuadores no solo del tipo inercial sino también dispositivos con otras características electromecánicas. El algoritmo seleccionado para determinar el conjunto final de valores en los parámetros topológicos del dispositivo puede ser caracterizado como un algoritmo genético y de su implementación se desprende un diseño óptimo desde el punto de vista de la optimización evolutiva multi-objetivo (EMOO).

## **Abstract**

In this work it is established a method to partially automate the design process for a capacitive accelerometer by implementing a bio-inspired meta-heuristic algorithm and starting from an analysis of the parameters participating in the modeling of the performance of an intertial sensor. Such sensor is intended to meet the requirements and design rules that enable its fabrication in the standard 0.5-micron CMOS process from which is obtained a monolithical micro-electromechanical integrated circuit in the fashion of the CMOS-MEMS devices. This research has a main interest in micro-sensors which transductive principle is related to the capacintance and electric potential variations associated with the floatinggate transistor (FGMOS), nevertheless, we anticipate suitability of the proposed methods and techniques to a variety of devices either inertially driven or with other electromechanical properties. The algorithm selected to determine the set of values for the topological parameters of the device can be characterized as a *genetic algorithm* and its implementation results in an optimal design as from the perspective of the evolutionary multi-objective optimization (EMOO).

# **Objetivo General**

Dar continuidad al trabajo realizado dentro del grupo de Sistemas VLSI respecto al diseño de sensores inerciales basados en el Transistor de Compuerta Flotante FGMOS, obteniendo a partir de las características y puntos de operación de este tipo de dispositivos, una metodología de automatización del diseño bajo los criterios de optimalidad dictados por la Optimización Evolutiva Multi-Objetivo.

## **Objetivos particulares**

- Profundizar en el modelado del transistor FGMOS como elemento principal de transducción de sensores inerciales, con base en los conocimientos previamente adquiridos en el diseño de circuitos integrados VLSI.

- Detallar las implicaciones que presenta el post-proceso de micromaquinado superficial utilizado para eliminar capas de sacrificio y liberar estructuras metálicas móviles, analizar el impacto sobre las propiedades mecánicas y eléctricas de circuitos integrados fabricados en tecnología CMOS, buscando minimizar componentes que comprometen su integridad.

- Realizar una revisión de los métodos clásicos de diseño iterativo y adaptar los mismos a una versión basada en objetivos en donde todas las características eléctricas y mecánicas puedan ser modeladas en términos de la geometría y la terminología topológica de layout como lo es la mínima longitud de diseño  $\lambda$ .

- Obtener un modelo dinámico pertinente para el estudio de un sensor integrado monolíticamente tal como el acelerómetro CMOS-MEMS.

- Generar el diseño y simulación de electrónica integrada para el acondicionamiento y procesamiento de señales a fin de tener un dispositivo sensor monolítico con señales de salida de fácil lectura y en acuerdo con los valores típicos de señal y alimentación de los sistemas comerciales.

- Participar activamente en la reciente tendencia de diseño óptimo automatizado, mediante el estudio, desarrollo e implementación de un algoritmo meta-heurístico bio-inspirado, como lo es en particular el *algoritmo genético*.

# Justificación

Ante la creciente demanda de dispositivos semiconductores dirigidos a la *sensorización* de ambientes y monitorización del bienestar personal, que en conjunto con las nuevas tecnologías de redes inteligentes, salud, movilidad y entretenimiento, el grupo de trabajo del Laboratorio VLSI decide dar continuidad a los proyectos de investigación en el área microsistemas, particularmente en el diseño, simulación y caracterización de sensores inerciales capacitivos basados en el transistor MOS de compuerta flotante dentro de un marco tecnológico y de fabricación de dispositivos micro-electromecánicos integrados CMOS-MEMS.

Derivado de los satisfactorios resultados que el grupo de trabajo ha obtenido en los últimos años siguiendo la hipótesis de factibilidad, conveniencia y oportuna aplicación del FGMOS como elemento principal de transducción en la conversión de movimiento mecánico acelerado a una proporcional señal eléctrica se propone en el presente trabajo profundizar en los siguientes rubros: 1. La composición de las capas metálicas que se encuentran disponibles en la tecnología de fabricación CMOS, su interacción con los decapantes necesarios para el post-proceso de micro-maquinado superficial y el impacto que tiene la presencia de ciertos materiales en el diseño micro-mecánico. 2. El modelado dinámico y respuesta a estímulos del acelerómetro capacitivo basado en tecnología CMOS-MEMS. 3. El modelado matemático del conjunto formado por el transductor integrado y la estructura capacitiva móvil propios de un acelerómetro CMOS-MEMS en términos enteramente geométricos y de topología. 4. Un análisis en la pertinencia del uso de los algoritmos metaheurísiticos bio-inspirados como una herramienta al alcance del ingeniero de diseño de circuitos integrados para automatizar bajo criterios de optimalidad la selección de parámetros de diseño.

Trabajos previos publicados tanto por el grupo de trabajo como por terceros sugieren una creciente integración de las denominadas técnicas de Optimización Evolutiva Multi-Objetivo en el desarrollo de circuitos integrados analógicos y digitales, habilitando al diseñador para encontrar una solución óptima en términos del mejor compromiso para dos o mas objetivos en conflicto, como lo son la reducción de área de diseño utilizada y el aumento de la sensitividad del instrumento. El presente trabajo estudia la novedosa implementación de un Algoritmo Genético en el diseño de un sensor MEMS, específicamente en el caso de un acelerómetro basado en el FGMOS y tomando en cuenta los factores de impacto antes mencionados como variables de los modelos matemáticos de los objetivos, criterios y restricciones de diseño. El resultado final de este trabajo es un algoritmo y una metodología de uso para automatizar parcialmente o totalmente el diseño de micro-sistemas.

El mencionado mecanismo computacional constituye una alternativa al método tradicional de diseño iterativo, lo cual podría repercutir positivamente en los tiempos y costos de las diferentes etapas de prototipado de sensores inerciales CMOS-MEMS.

## Capítulo 1

## Introducción

Al paso de los años la tecnología de circuitos integrados se ha diversificado enormemente dando lugar a una gran cantidad de dispositivos con características muy variadas y que se añaden día con día a un sin fin de aplicaciones. Los denominados sistemas micro-electromecánicos (MEMS) o también llamados "micro-sistemas", si bien en un sentido más amplio no están directamente catalogados como circuitos integrados, comparten con estos muchos de los procesos y herramientas que permiten su creación, incluyendo pero no limitándose a plataformas de diseño, técnicas de fabricación y métodos de caracterización. Es así que los sistemas micro-electromecánicos tienen en esencia la morfología de un circuito integrado, tal como lo es contar con un sustrato, generalmente cristalino, y un conjunto de capas metálicas superpuestas por encima de la superficie del mismo y que a su vez se separan unas de otras por medio de depósitos de material dieléctrico.

El atributo más significativo de los dispositivos MEMS en general y que con certeza los distingue de los circuitos integrados convencionales, es su capacidad de interactuar con su medio circundante no solo a través de señales eléctricas sino por medio de variedad de estímulos mecánicos, electromagnéticos y químicos, entre otros. Se puede decir entonces, que

ya sea tanto a escala macroscópica como microscópica, dependiendo de la aplicación, el micro-sistema buscará producir y/o percibir señales de una naturaleza *física* tales como lo son un desplazamiento mecánico, un cambio de presión, una reacción química o la presencia de radiación y partículas. Tal como se puede ver en (Abarca-Jiménez et al. 2018), (Reyes Barranca et al. 2010) y (Domínguez-Sánchez et al. 2017), trabajos previos que han emanado de este grupo de investigación han abordado y verificado la aplicación de sistemas micro electromecánicos en la medición o aprovechamiento de algunas de la mencionadas magnitudes físicas.

En el presente trabajo así como en los antes citados destaca el uso del transistor MOS de compuerta flotante (FGMOS) cuyo mecanismo es de uso generalizado en circuitos de muy alta escala de integración (VLSI) y su sencillez en términos de diseño topológico lo vuelven un fuerte candidato para explorar el uso de algoritmos heurísticos y así proponer una solución óptima en términos numéricos partiendo de un conjunto de objetivos de diseño que se busca satisfacer. Entonces, a continuación se presentan las generalidades del diseño VLSI y se detalla el proceso de diseño de un sensor inercial CMOS-MEMS, se analizan las propiedades funcionales de un acelerómetro de características típicas, se propone el modelado matemático de un conjunto de metas y restricciones de diseño y describe la implementación de una metaheurística bio-inspirada para consolidar un diseño semi-automatizado en contraste con un diseño convencional.

#### 1.1 Antecedentes

El desarrollo de las técnicas de fotolitografía, ataque químico y de depósito y crecimiento de películas de diversos materiales llevó a mediados del

siglo XX a la concepción y fabricación de los primeros dispositivos integrados. Este acontecimiento forma parte del nacimiento de una industria que no ha detenido su expansión y crecimiento hasta nuestros días y cuya relevancia en la actualidad es total, siendo que la economía, la educación, la salud y el entretenimiento dependen enormemente de la industria electrónica y cada una de ellas avanza en la medida que esta última lo hace.

Un circuito integrado es, en el sentido más amplio, un conjunto de dispositivos electrónicos, tanto activos como pasivos, que residen sobre el mismo sustrato, logrando así interconexión directa y el máximo aprovechamiento del espacio, ya sea área o volumen, designado para la tarea a realizar. Es especialmente relevante cómo a través de los años se han superado constantemente los límites tecnológicos y se ha llegado a una descomunal densidad de componentes por centímetro o milímetro cuadrado del sustrato llegando a la necesidad de clasificar a estos dispositivos en función de la denominada escala de integración. La escala de integración mide esta densidad y hablar de una alta (LSI) o muy alta escala de integración (VLSI) nos permite estimar las capacidades que dicho dispositivo tendrá una vez en operación.

Cuando se habla de un dispositivo integrado VLSI se habla de miles y hasta millones de dispositivos activos individuales que coexisten dentro de la misma plataforma, habilitando al diseñador para ejecutar aplicaciones con un alto grado de complejidad con un consumo relativamente bajo de energía. Estos dispositivos, sin embargo, por su reducido tamaño y características eléctricas requieren de una muy sofisticada red industrial y logística que, a través de muy altos estándares de calidad, permite la fabricación y manejo de elementos altamente sensibles a la contaminación y condiciones ambientales. Detrás de cada circuito integrado o microchip, como también se le conoce, existe una cadena de

Figura 1.1: Resumen del proceso de obtención de obleas de silicio cristalino.

valor que extrae y transforma minerales y otros recursos naturales, los purifica y manipula a nivel prácticamente atómico para formar estructuras funcionales que denotan una sinergia sin precedentes y que ponen a nuestro alcance, de manera práctica, los fenómenos que solo se explican por medio de un profundo análisis de las interfaces entre materiales y las propiedades electrónicas de los mismos. La primera etapa del proceso industrial se resume en la Figura 1.1. El camino de la denominada tecnología CMOS recién obteniendo una placa de silicio puro y cristalino también conocida como oblea, la misma usualmente se encuentra disponible comercialmente con un dopaje inicial de baja concentración de impurezas tipo p o tipo n, lo que sirve como base para producir en ella transistores de efecto de campo canal N y canal P, respectivamente.

#### 1.1.1 Tecnología CMOS convencional

Dentro de los llamados transistores de efecto de campo existe un tipo cuyo desarrollo se ha visto potenciado gracias a sus características como lo son un bajo consumo de potencia y una muy marcada compatibilidad con los procesos de fabricación planar (basada en el depósito de películas delgadas superpuestas), el MOSFET (Metal-Oxide-Semiconductor Field-Effect Transistor). Este es un dispositivo noble que presenta un conveniente comportamiento lineal o exponencial según los potenciales que se

Figura 1.2: Terminales del transistor MOSFET canal P y canal N, y proceso de formación del canal.

apliquen en sus terminales. De manera ideal, su característica de salida permite controlar la magnitud de una corriente eléctrica (entre drenador y fuente) en función de un voltaje de entrada (potencial que se aplica a la terminal de compuerta). A medida que el potencial en compuerta (gate) se incrementa en magnitud, los portadores de polaridad contraria que se encuentran en el sustrato se ven atraídos y comienzan a formar un canal que comunica las terminales de drenador (drain) y fuente (source) (Figura 1.2). Sin embargo esta estructura en su forma más simple permite trabajar únicamente dentro de un rango estrecho de voltajes que limita sus aplicaciones tanto analógicas como digitales, esto se soluciona interconectando dispositivos MOS con ambos tipos de polaridad (canal N y canal P).

Una innovación que permitió a las obleas de silicio y por ende a los circuitos integrados en general acceder a dispositivos de mayor complejidad circuital tales como compuertas lógicas y amplificadores fue la introducción del denominado *pozo*, el cual se obtiene a través de una combinación de procesos de fotolitografía y de implantación iónica y consiste en obtener una región de conductividad contraria dentro de la previamente dopada superficie de la oblea, es decir, generar una pequeña porción de sustrato tipo N sobre la oblea tipo P o viceversa (Figura 1.3). En general al tratar señales tanto analógicas como digitales es conve-

Figura 1.3: Transistores MOS complementarios en un mismo sustrato.

niente contar con dispositivos MOS complementarios o CMOS, es decir, que combinan ambos tipos de transistor MOS, ya que pueden manipularse de una manera más precisa los puntos y regímenes de operación de cada uno de los dispositivos.

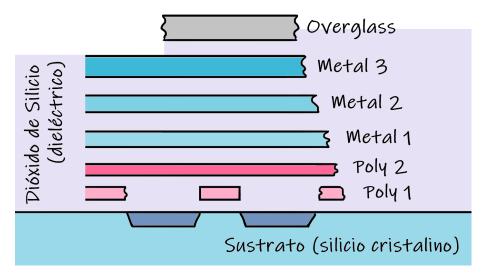

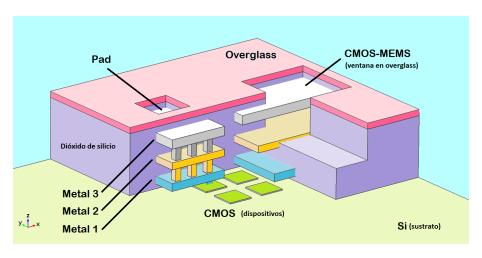

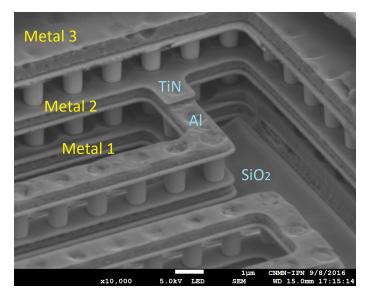

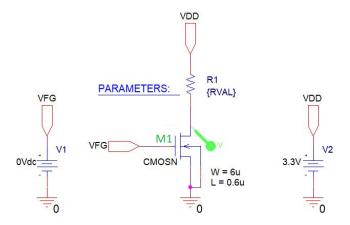

Otro aspecto importante al seleccionar el proceso con el que se va a trabajar en el marco de la tecnología CMOS es la cantidad de capas metálicas disponibles que permiten la interconexión entre dispositivos. En el caso particular de este trabajo la tecnología base para todos los diseños e implementaciones es la tecnología C5 de ON Semiconductor, la cual se caracteriza por aceptar una longitud de canal mínima de  $0.6\mu m$  en los transistores MOS y por contar con dos capas de silicio policristalino (Poly) y tres más de una aleación metálica por encima del sustrato, lo que la clasifica como una tecnología 2P3M. Dichas capas se interconectan por medio de vias (pequeños nodos verticales que hacen contacto con dos capas a la vez) y es en general la capa inferior de Poly la que se emplea para producir la compuerta de los transistores MOS como se observa en la Figura 1.4. Las capas de polisilicio cuentan con una alta concentración de portadores por lo que se les considera cuasimetales. Tanto las capas de polisilicio como las de metal se encuentran embebidas en un depósito de dióxido de silicio, el cual las envuelve completamente y cumple la función de un aislante eléctrico. Por encima de todo se encuentra una capa protectora de nitruro de silicio llamada Overglass, esta capa es un vidrio que protege a los dispositivos del ambiente

Figura 1.4: Capas disponibles en el proceso de fabricación C5 de ON Semiconductor.

y solo cuenta con aberturas en las posiciones por encima de los nodos de conexión con el exterior. Para acceder a estos nodos también conocidos como *pads* se expone la capa superior de metal denominada Metal 3 a través de un proceso de ataque por iones reactivos (RIE). La utilidad de las tres capas metálicas en la formación de estructuras MEMS se expone a continuación, sin embargo, su composición y propiedades es motivo de una más amplia discusión en apartados posteriores.

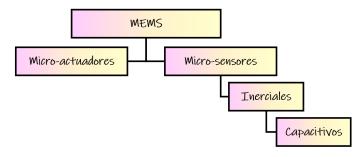

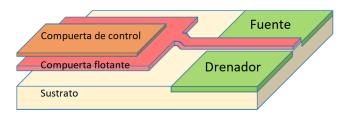

### 1.1.2 Dispositivos MEMS y CMOS-MEMS

Los micro-sistemas se pueden clasificar de diferentes formas, por ejemplo, en función de su utilidad, ya sea como micro-sensores o micro-actuadores, es decir, convirtiendo una señal física externa en una señal eléctrica o viceversa, respectivamente. También es posible clasificarlos de acuerdo a su *principio de transducción*, es decir, conociendo cuál es la magnitud física que se intercambia con una señal eléctrica, de esta manera los hay capacitivos, térmicos, químicos, etc.

Figura 1.5: Clasificación del acelerómetro capacitivo.

Figura 1.6: Acelerómetro capacitivo y sistema masa-resorte equivalente.

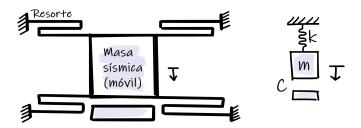

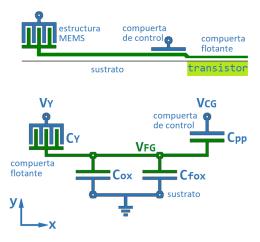

El objeto de estudio en este caso es un acelerómetro capacitivo que entra dentro de la categoría de micro-sensores inerciales que se muestra en la Figura 1.5. Los sensores inerciales relacionan una variable eléctrica con un desplazamiento acelerado debido a una fuerza externa aplicada. En este caso, lo que se obtiene es una variación en la capacitancia presente entre dos elementos metálicos. Esto generalmente se logra haciendo suspender un bloque móvil de masa m relativamente grande y que se sujeta a un juego de resortes con rigidez equivalente k a la vez que respecto a un segundo bloque fijo, también metálico, se forma un capacitor variable, también llamado varactor, de capacitancia C. La capacitancia varía de manera inversamente proporcional a la distancia que separa los bloques, misma distancia que es proporcional a la fuerza, aceleración y desplazamiento que experimenta la también llamada *masa sísmica* (Figura 1.6).

Figura 1.7: Alambrado externo entre dados independientes.

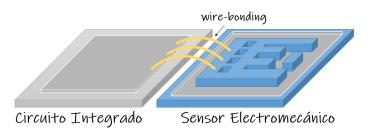

La idea de fabricar dispositivos MEMS incluyendo estructuras tales como vigas, resortes y engranajes a nivel microscópico utilizando un proceso similar al de fabricación de circuitos integrados (basado en una sucesión de depósitos metálicos y fotolitografía) no es nueva y ha estado desarrollándose de manera parcialmente independiente a la par de la tecnología CMOS. Existe una variedad de plataformas donde no se construye ningún elemento electrónico activo sobre el sustrato que controle o detecte las señales, en cambio, se fabrican estructuras puramente electromecánicas con las dimensiones y materiales apropiados para cada aplicación, de ahí surge la necesidad de conectar circuitos electrónicos externos para llevar a cabo el acondicionamiento, lectura e interpretación de las señales, usualmente un circuito integrado adjunto. Si bien ambos dispositivos pueden ser encapsulados juntos para su presentación comercial final, es necesario realizar un paso intermedio que consiste en un proceso de alambrado que comunica pads de ambos dispositivos, a este proceso se le conoce como wire-bonding (Figura 1.7) y es similar al que se utiliza para comunicar a cualquier chip con los pines de su encapsulado final.

Una alternativa es por supuesto, proponer un diseño electromecánico compatible con las capas metálicas de la tecnología CMOS, las cuales originalmente están concebidas únicamente para la interconexión de componentes. En caso de utilizarse dichas capas para implementar también

Figura 1.8: Integración monolítica CMOS-MEMS.

las estructuras electromecánicas de un MEMS, se habla entonces de un dispositivo CMOS-MEMS. Con esto se facilita la integración del elemento transductor con los componentes electrónicos y de procesamiento de señal en un mismo dado (corte de la oblea con un circuito integrado individual) tal como se aprecia en la Figura 1.8.

Existen casos en los que la estructura MEMS, además de no sobrepasar una determinada área de diseño en milímetros cuadrados, resulta ser totalmente compatible con las capas y materiales disponibles en el proceso de fabricación CMOS estándar. Teniendo en cuenta el análisis que se realiza en (Kaajakari 2009) se puede afirmar que entre las ventajas que conlleva integrar de manera monolítica el dispositivo CMOS-MEMS sobresalen una reducción en las capacitancias parásitas, una reducción en los costos de interconexión y encapsulado, un significativo aumento en el rédito de piezas por oblea y en general una mayor sinergia entre dispositivos, todo esto ejerciendo contrapeso ante a una limitada variedad de aplicaciones y la necesidad de procesos adicionales posteriores a la fabricación.

Una vez que se opta por conjuntar monolíticamente ambos subsistemas, es decir, la electrónica integrada y la estructura micro-electromecánica, surge la necesidad de liberar esta última de las restricciones mecánicas que supone el dieléctrico propio de la fabricación CMOS. Para retirar efectivamente el volumen de dióxido que envuelve a las ca-

Figura 1.9: Liberación de un resorte metálico.

pas metálicas se recurre usualmente a un ataque químico basado en ácido fluorhídrico (HF) adicionado con compuestos que lo hacen más selectivo y disminuyen su razón de ataque sobre el aluminio, componente principal de las capas metálicas disponibles. Para poder efectuar este ataque es necesario considerar en el diseño una ventana abierta en la capa de Overglass por encima de la estructura que se desea liberar. A este proceso se le conoce como micro-maquinado superficial pues sucede principalmente por encima de la superficie del sustrato. En oposición nos encontramos con el micro-maquinado volumétrico en el cual se busca atacar al sustrato mismo (silicio cristalino) para formar membranas y ventanas útiles en otro tipo de aplicaciones.

Tras una exitosa disolución del dióxido de silicio y como se puede observar en la Figura 1.9, las estructuras mecánicas quedan expuestas y libres para desplazarse salvo en sus puntos de anclaje. Esto permite producir vigas y resortes que responden de manera conveniente a las aceleraciones presentes aunque también de manera indeseada a esfuerzos residuales del proceso de fabricación.

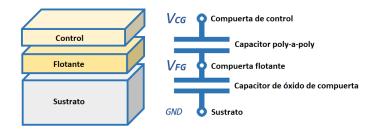

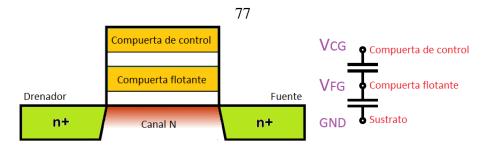

Figura 1.10: Transistor de compuerta flotante.

#### **1.1.3 FGMOS**

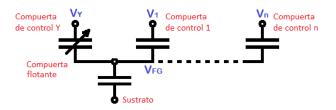

Los transistores de compuerta flotante, así como otros dispositivos de la familia CMOS, se diseñan configurando capas de distintos materiales en una estructura topológica determinada. El transistor MOS de compuerta flotante, también conocido como FGMOS, ha sido principalmente utilizado en la fabricación de dispositivos de almacenamiento digital (Baker 2005 pp. 113,466). En dicho caso, la información se coloca dentro del dispositivo en forma de carga eléctrica que se transfiere hacia y desde (programación y borrado) la llamada terminal de compuerta flotante. La característica principal del FGMOS es incluir una estructura de doble compuerta de polisilicio (Figura 1.10), apiladas una sobre otra y donde la más cercana al canal se encuentra aislada eléctricamente de todas las otras terminales y pads, sin embargo, la terminal flotante puede ser inducida electrostáticamente para alcanzar un potencial que de hecho será el responsable de formar el canal y controlar la conducción de corriente a través del transistor.

### 1.1.4 Metaheurísticas bio-inspiradas

Se conoce como heurística a los mecanismos de búsqueda computacionales que pretenden encontrar, dentro de un espacio multidimensional de variables, la solución o conjunto de soluciones que mejor comportamiento presenten ante una *función objetivo*. La función objetivo es el modelo matemático de un parámetro de desempeño dependiente de una o más de las variables en el problema de ingeniería. Usualmente se busca minimizar o maximizar a una o varias de las funciones objetivo de manera que se alcance un óptimo, ya sea local o global, en el desempeño general de la solución. Existe un tipo de heurística que va *más allá* del dominio numérico incorporando ideas tomadas directamente de la naturaleza, en partícular imitando al comportamiento de entes vivientes y es por eso que se les conoce como metaheurísticas bio-inspiradas.

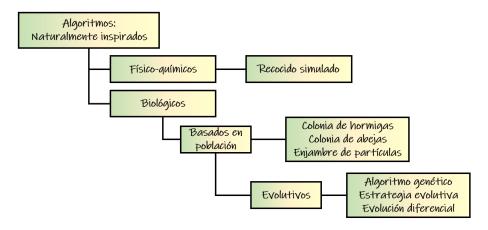

Dentro del campo de la *optimización multi-objetivo* y en particular de los sistemas naturalmente-inspirados, existe una amplia variedad de técnicas que se pueden clasificar de acuerdo a su elemento principal que es en el cual basan su inspiración y conceptos. Existen algoritmos que recuerdan y emulan la forma en que se comportan las poblaciones, ya sea la trayectoria que siguen grupos de individuos (particle swarm), la forma en la que estos consiguen su alimento (ant colony, artificial bee colony) o incluso la manera en que la información genética cambia a través del tiempo (genetic algorithms, evolutionary strategy). Existen también los sistemas que imitan procesos físico-químicos por lo que se les considera naturalmente-inspirados. En la Figura 1.11 se resumen brevemente los mecanismos más allegados al presente trabajo.

Este caso de estudio representa una aproximación a la Optimización Evolutiva Multi-Objetivo (EMOO) con aplicación en el campo del diseño de layout CMOS. Si bien los algoritmos bio-inspirados del estado del arte usualmente atienden problemas computacionales bastante sofisticados (no siempre en el dominio de la ingeniería y el mundo real) y se refuerzan y mejoran continuamente comparándose unos con otros. Los parámetros y características del algoritmo seleccionado para el presente desarrollo no pretenden mejorar el desempeño del algoritmo en sí, sino apoyar al ingeniero de diseño en la búsqueda de un diseño preliminar razonablemente óptimo bajo un conjunto de criterios y establecer el método correspondiente para validar los resultados.

Figura 1.11: Resumen de algoritmos naturalmente inspirados más comunes.

#### 1.1.5 Algoritmos genéticos

Los llamados algoritmos genéticos son un versátil grupo de técnicas metaheurísticas bio-inspiradas basadas en el proceso evolutivo natural, al cual emulan computacionalmente y que a través de la optimización evolutiva multi-objetivo son comúnmente utilizados en problemas de optimización en ingeniería (Coello 2015) y en diversos problemas de logística (Murata et al. 1996). Este tipo de métodos iterativos de búsqueda son bien conocidos por manejar de manera efectiva grandes cantidades de parámetros de modelado en problemas con hasta unos pocos miles de variables (Yang et al. 2008) y hasta un par de docenas de funciones objetivo (Lopez-Jaimes et al. 2015). Esto hace a la EMOO un campo de investigación fértil en la actualidad. Otro tópico relevante dentro de este contexto es el apropiado manejo de restricciones durante el modelado matemático de un problema particular, esto se debe a las múltiples limitaciones naturales y tecnológicas que los problemas de diseño de ingeniería usualmente involucran.

Cuando se trata con un problema de diseño en ingeniería, ya sea mecánico, microelectrónico o algún otro predominantemente basado en la geometría, especialmente aquellos donde la forma y relación de aspecto de los elementos diseñados puede ser deconstruida en partes más pequeñas y fundamentales, y donde cada una de estas partes cuenta con un conjunto particular de parámetros. La decisión de utilizar algoritmos genéticos se relaciona con sus ya conocidos mecanismos para la codificación, manipulación y selección iterativa de parámetros que de otra manera son ajustados manualmente por el diseñador. El algoritmo es en sí mismo un sofisticado intento de emular computacionalmente el complejo proceso biológico mediante el cual una determinada población de individuos combina su información genética buscando alcanzar cierta ventaja o incremento en el desempeño de alguna tarea ante una situación dada conforme pasa el tiempo y cada generación sustituye a la anterior.

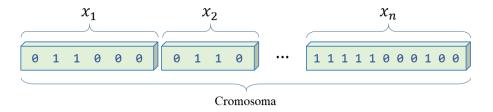

En términos de un algoritmo genético, cuando éste se aplica a un problema de diseño de ingeniería, cada una de las variables es codificada en cierto número de bits, usualmente una cadena binaria lo suficientemente larga y acorde con la naturaleza física de la variable y su rango de utilidad en los números reales dentro del espacio de búsqueda del algoritmo. Llamamos *cromosoma* (Figura 1.12) al arreglo de n variables convenientemente definidas en longitud y posición que son concatenadas en una sola cadena binaria. Este arreglo contiene todas las variables que se desprenden del modelo matemático del problema para cada una de las funciones objetivo. Un cromosoma a su vez representa a un *individuo* de entre la población, siendo que cualquiera de sus características particulares puede ser extraída de la secuencia de bits y utilizada para evaluar numéricamente las funciones objetivo asociadas con los requerimientos del diseño.

Para un problema con un solo objetivo, cuando se evalúa una combinación particular de valores de las variables, ya sea continuos o discretos, la función objetivo de n variables de la expresión 1.1 describe la

Figura 1.12: Cromosoma incluyendo todas las variables codificadas en una misma cadena binaria.

llamada *aptitud* del individuo seleccionado, esto es, qué tan bien el individuo se desempeña cuantitativamente para alcanzar el objetivo modelado. Durante el proceso evolutivo los individuos son seleccionados aleatoriamente y probados evaluando la función objetivo con sus valores para determinar su aptitud, además, se implementan mecanismos para determinar cuál elemento de entre la población es el de mejor desempeño en una generación dada (elitismo). Algunos otros operadores que usualmente se utilizan son la *mutación*, consistente en alterar arbitrariamente el código genético de un individuo para desviar su tendencia evolutiva, evitando caer en máximos o mínimos locales y la *cruza* para combinar características e información genética de dos o más individuos interpolando sus cromosomas. Como resultado iterativo de los procesos mencionados, se produce, al paso de las generaciones, un acercamiento a un óptimo global.

fitness =

$$f(x_1, x_2, ..., x_n)$$

(1.1)

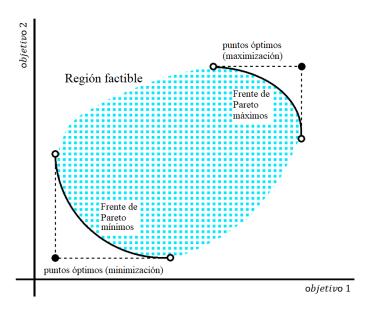

En el caso de una tarea de diseño multi-objetivo, es útil implementar este tipo de métodos evolutivos cuando todos y cada uno de los objetivos que se persiguen implican algún tipo de conflicto entre ellos, de manera que incrementar la aptitud o desempeño para una meta en particular va en detrimento de las demás. Esta es la razón por la que un análisis de Pareto se añade al proceso para encontrar a la mejor solución y no nece-

Figura 1.13: Ubicación de los frentes de Pareto y los puntos óptimos ideales (utópicos).

sariamente a un óptimo ideal. La mejor solución es aquella con la mejor relación o compromiso entre dos o más objetivos. Usualmente el punto más cercano del *frente de Pareto* a la solución ideal es la que se selecciona como la solución final, pues para un problema con dos objetivos como el que se muestra en la Figura (1.13) el óptimo global no puede ser alcanzado en ambos objetivos al mismo tiempo (Coello 2001). El frente de Pareto se construye a partir del conjunto de *soluciones no dominadas* para un espacio de búsqueda determinado. Una solución no dominada es aquella para la cual no existe alguna otra solución que sea mejor (en aptitud) en todos los atributos a la vez. Esta solución domina a algunas otras siendo mejor en al menos uno de los objetivos e igual o mejor en todos los demás.

#### 1.2 Estado del arte

#### 1.2.1 Dispositivos comerciales y proyectos académicos

Una gran variedad de dispositivos de medición inercial están disponibles en el mercado, se cubre de manera prácticamente total todo el espectro de aplicaciones, lo que permite contar con dispositivos de gama baja principalmente pensados para el ámbito académico de pre-grado y también con sensores de alta calidad con especificaciones apropiadas para sistemas de instrumentación científica, industrial y militar.

Al momento de adquirir un dispositivo inercial y en particular un acelerómetro es conveniente destacar las especificaciones básicas para ubicar adecuadamente a los candidatos. Entre estos requerimientos a cubrir se encuentran el rango de operación, es decir, los límites dentro de los cuales la lectura es confiable, la resolución y sensitividad del dispositivo, las cuales permiten calcular la señal eléctrica de salida que corresponde a un determinado estímulo y los valores de alimentación, que determinan el consumo de energía de cada elemento. Un análisis de 64 acelerómetros disponibles en el mercado en el año 2019 arroja las siguientes estadísticas:

- Rangos de aceleración: 1 G 120 G

- Valores de alimentación: 3 V a 6 V (más comunes 3.3 V y 5 V).

- Consumo de corriente: 700 nA 24 mA

- Resolución en dispositivos digitales: 10 24 bits

- Sensitividad: 5 mV/G@100 G a 1 V/G@1.7 G

Uno de los principales criterios de selección es la compatibilidad con sistemas analógicos o digitales, lo cual suele estar dado en función de la aplicación (Figura 1.14).

Figura 1.14: Distribución de mercado de acelerómetros comerciales.

En cuanto a trabajos académicos relacionados con el desarrollo de sensores inerciales y en particular con acelerómetros de 1 o 2 ejes con fabricación MEMS y CMOS-MEMS, un análisis resumido en la Tabla 1.1 muestra una mayoría de implementaciones en el rango de las bajas aceleraciones y una sensitividad en el orden de 1V, ambas características coinciden con los alcances y objetivos del presente trabajo.

| Sensitividad | Rango de operación | Publicación       |

|--------------|--------------------|-------------------|

| 1.22 V/G     | ±3 G               | Yuntao 2009       |

| 2.1 V/G      | 10 G               | Chih-Ming 2009    |

| 0.1 μA/G     | ±33 G              | Benxian 2009      |

| 0.7 V/G      | _                  | Kim 2012          |

| 0.4 fF/G     | 7.5 G              | Daisuke 2014      |

| 0.8 fF/G     | 6 G                | Sheng-Hsiang 2014 |

| 0.6 V/G      | 1 G                | Daisuke 2015      |

| 0.13 V/G     | 20 G               | Gonseth 2015      |

| 20 fF/G      | 20 G               | Yamare 2015       |

| 1.78 V/G     | 0.1 G              | Kevitha 2016      |

| 0.8 V/G      | ±2 G               | Granados 2017     |

| 35 fF/G      | ±5 G               | Zakriya 2018      |

Tabla 1.1: Resumen de trabajos académicos basados en acelerómetros MEMS y CMOS-MEMS

## 1.2.2 Uso de algoritmos genéticos en el diseño de circuitos integrados

Si bien los dispositivos analizados y mostrados previamente corresponden al sector comercial y sus métodos de diseño y fabricación no son de dominio público, al igual que en el presente trabajo, se han estado llevando a cabo esfuerzos para integrar la filosofía, elementos y conceptos de la optimización computacional heurística en el proceso de diseño de sensores inerciales.

De una manera particularmente interesante para el contexto del presente trabajo, se puede encontrar que en los reportes de Melnik et al, Darnobyt et al y Kryvyy et al, se propone respectivamente lo siguiente: un sistema para optimizar dimensiones de un acelerómetro MEMS que alcance ciertos estándares de sensitividad y robustez que se validan mediante simulación multifísica en ANSYS, permitiendo mediante un script automatizar el análisis modal (Melnyk et al. 2013), un algoritmo para diseñar módulos MEMS generales, tales como micro-actuadores, microsensores y etapas de acondicionamiento, con base en su geometría y dimensiones (Darnobyt et al. 2008) y un análisis de los factores que determinan la efectividad de un algoritmo genético como parte del diseño de un sistema micro-electromecánico (Kryvyy et al. 2009).

De manera similar, en los trabajos previos de nuestro grupo se promueve la noción de compatibilidad entre los dispositivos CMOS-MEMS y los algoritmos genéticos, más específicamente con miras al desarrollo de dispositivos monolíticos basados en el transistor MOS de compuerta flotante (Granados-Rojas et al. 2018) y más adelante se propone analizar lo que sería una relación viable entre las dimensiones y la rigidez de un resorte de vigas útil para el sistema masa-resorte de un acelerómetro CMOS-MEMS convencional, esto con base en la optimalidad de Pareto (Granados-Rojas et al. 2020).

## 1.3 Conclusiones del capítulo

La tecnología CMOS-MEMS es una alternativa viable para la generación de dispositivos de instrumentación inercial, especialmente en proyectos académicos con recursos limitados. Dicha tecnología híbrida habilita a investigadores e ingenieros de diseño independientes para acceder a un prototipo MEMS de bajo costo que permita realizar pruebas de concepto.

Se retoma como elemento vínculo entre las tecnologías CMOS y MEMS al transistor de compuerta flotante. Dicho dispositivo permite integrar capacitores variables dentro de un elemento activo de manejo de corriente, por lo que se consolida su naturaleza como transductor principal dentro de la línea de investigación del grupo de trabajo.

En general, para tratar con problemas de diseños topológico y de predominante carácter geométrico como lo son los habituales en diseño mecánico y micro-electrónico, los algoritmos de cómputo evolutivo y en particular los algoritmos genéticos son de singular relevancia. La idea fundamental de dichos algoritmos es codificar variables físicas en cadenas numéricas discretas con las cuales se puede realizar un proceso de optimización ya sea heurística o meta-heurística. Siendo el diseño topológico de micro-dispositivos una técnica con valores usualmente discretos (múltiplos enteros de un tamaño mínimo de característica), el algoritmo genético tradicional parece ser una herramienta ad-hoc para realizar la búsqueda automática de parámetros que satisfagan la previamente definida función objetivo.

## Capítulo 2

# Aspectos teóricos

#### 2.1 Acelerometría

Como se ha mencionado antes, los MEMS, también llamados microsistemas se clasifican en dos grandes grupos, uno de ellos dedicado a proponer diversos tipos de sensores y módulos de detección por lo que en general se les denomina micro-sensores. Uno de los más comunes tanto en el mercado como en el contexto académico dado su amplio espectro de aplicaciones es el acelerómetro. El acelerómetro es el dispositivo electrónico ideado para trasladar una magnitud física inercial como lo es la aceleración a una cantidad eléctrica, la cual finalmente se reinterpreta ya sea como una aceleración en sí misma o como una proporción del efecto que tiene la gravedad sobre el dispositivo y que influye de una manera u otra en medida de la posición angular del mismo.

Es común encontrar a los acelerómetros acompañados de otros dispositivos de naturaleza similar, ya que a través de la denominada fusión de sensores es posible determinar características de un sistema dinámico que por separado no resultan totalmente accesibles. Este es el caso de la IMU, que por sus siglas en inglés se refiere a una Unidad de Medición In-

Figura 2.1: Unidad de medición inercial

ercial. La unidad IMU convencional incluye, mas no está limitada, a los siguientes elementos: acelerómetros, giroscopios y brújulas electrónicas (magnetómetros). Es por ello que resultan particularmente útiles y de uso común en aplicaciones de navegación autónoma y robótica móvil.

Los acelerómetros capacitivos basan su funcionamiento en una secuencia de transducciones que permiten pasar desde una aceleración y por tanto un desplazamiento mecánico hasta un valor de voltaje o señal digital. Si bien no toda la trayectoria de esta secuencia representa una transducción completamente lineal, podemos afirmar que efectivamente la magnitud de la señal eléctrica de salida es proporcional a la magnitud de la aceleración.

#### 2.2 Sensitividad

Un parámetro de especial relevancia dentro de los sensores en general es la sensitividad, la cual nos indica qué magnitud alcanzará la señal eléctrica de salida de un micro-sistema ante un estímulo unitario de la señal de entrada. Es decir, se relaciona ampliamente con la función de transferencia del sistema y nos ofrece un criterio para seleccionar de entre una variedad de dispositivos dependiendo del rango dinámico de la aplicación. En un acelerómetro una alta sensitividad no es necesariamente deseable, sino que ésta debe ser acorde con la máxima magnitud conocida de aceleración a la que se someterá el dispositivo durante su

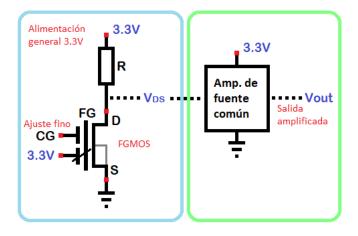

aplicación. Una alta sensitividad permite alcanzar valores de tensión o corriente eléctrica lo suficientemente amplias para su medición, a partir de aceleraciones relativamente pequeñas. Por el contrario, una sensitividad baja puede llegar a ser útil en ambientes donde se sabe que interesan estímulos de gran magnitud que requieren poca amplificación para ser detectados y transducidos al dominio eléctrico. La sensitividad S puede interpretarse entonces como la ganancia del micro-sistema y como se verá más adelante, para fines específicios de este proyecto se considera como la razón de cambio en la corriente de drenador de un transistor MOS de compuerta flotante, en función de los cambios de capacitancia de una estructura MEMS.

Tomando en cuenta la aceleración g como la que produce la gravedad de la tierra ( $g = 9.81 \text{m/s}^2$ ), en micro-sistemas analógicos pensados para trabajar con baja aceleración (hasta un par de veces la aceleración g), una sensitividad apropiada se encontraría en el orden de 1V/g, es decir, el sistema entrega un voltaje que equivale ya sea a una fracción significativa o un pequeño múltiplo de 1 volt, cuando sobre el dispositivo se ejerce hasta una vez la aceleración g. Una tensión así es facilmente detectable junto con sus variaciones de hasta unos pocos milivolts por la siguiente etapa en el sistema de medición. Dicha siguiente etapa puede ser algún acondicionamiento adicional (amplificación, filtrado, etc.) o incluso un convertidor analogico-digital (ADC) para integrar el acelerómetro como elemento de percepción a un sistema digital mayor. Existen por otro lado, sensores que monolíticamente asumen también la digitalización de la señal, por lo que su salida no es directamente un voltaje analógico sino una cantidad numérica discreta, en este caso, además de la sensitividad se vuelve relevante el concepto de resolución.

La resolución es la cantidad mínima de variación en la señal de entrada que al ser detectada produce un cambio en la salida. Por lo tanto es común encontrar la resolución de un acelerómetro digital expresada

como cierta cantidad N de LSB/g, donde LSB se refiere por sus siglas en inglés al bit menos significativo de una cuenta binaria y N es la cantidad de cifras que avanzó la cuenta binaria ante una aceleración equivalente a g. En otras palabras, la minima aceleración que se puede percibir con un dispositivo digital sería g/N m/s² y por tanto aquella donde la cuenta digital se incrementa o disminuye de un entero binario al siguiente.

#### 2.3 Sistema masa-resorte

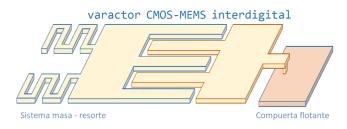

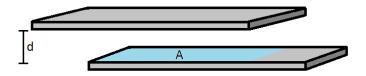

La tecnología conocida como CMOS-MEMS combina en un mismo chip (dado de silicio) las capacidades de ambas tecnologías, es decir, la circuitería CMOS convencional y las estructuras de los sistemas microelectromecánicos (MEMS). Cuando se habla de sensores inerciales, la micro-estructura básica utilizada para medir aceleración tiene la morfología de un sistema masa-resorte, acoplado a uno o más capacitores variables cuya capacitancia cambia proporcionalmente al desplazamiento de la masa, también llamada masa sísmica por su comportamiento oscilatorio. En la medida en que esta masa sísmica incrementa su proximidad a alguna otra placa metálica, es decir, la distancia d que las separa se reduce, la capacitancia (ecuación 2.1) del capacitor de placas paralelas crece. La capacitancia es por otra parte, también proporcional al área A de las placas o superficies que se enfrentan y a la permitividad eléctrica  $\epsilon$ del medio ( $\epsilon_0$  para aire o vacío). La configuración que presentan en conjunto el sistema masa-resorte (móvil) y el capacitor variable se muestra en la Figura 2.2.

$$C = \frac{\epsilon_0 A}{d} \tag{2.1}$$

Como se mostró en (Granados-Rojas et al. 2016) las estructuras capacitivas empleadas podrían no ser tan simples como un capacitor de

Figura 2.2: Esquemático de una estructura típica basada en un sistema masa-resorte MEMS para un sensor inercial.

placas paralelas, en cambio, se puede aprovechar las cantidad de capas metálicas con las que cuenta el proceso de fabricación para generar intrincadas estructuras tridimensionales con múltiples componentes capacitivas. Sin embargo, dichas estructuras pueden llegar a tratarse como la superposición de varios capacitores de placas paralelas en los cuales al despreciarse los efectos de borde aún se conserva una aproximación bastante cercana al efecto total.

En el proceso CMOS-MEMS y en particular para un acelerómetro, una vez teniendo un chip CMOS previamente diseñado y fabricado para llevar a cabo las tareas de control electrónico y de procesamiento de señales, se procede a un post-proceso de ataque ya sea físico o químico para eliminar las capas de dieléctrico que rodean a las estructuras MEMS (capas de sacrificio) y así permitirles libre movimiento ante la presencia de un movimiento acelerado. Como es de esperarse estas estructuras metálicas son de hecho las capas metálicas disponibles en el proceso para la interconexión de componentes, también conocidas como capas estructurales. Como se analizó en Granados-Rojas et al. 2019 y se presentará más adelante, la composición de estas capas varía de acuerdo con el proceso de fabricación y en particular para el proceso C5 se cuenta con una película externa de nitruro de titanio (TiN) que impacta en la rigidez, masa, conductividad y durabilidad de los elementos electromecánicos.

Sin embargo, la gran mayoría de los procesos de fabricación cuentan únicamente con el material base que consiste en una aleación de aluminio (Al) y cobre (Cu) con este último en una proporción menor al 5%, razón para realizar cálculos y estimaciones alrededor de las propiedades del aluminio puro en la mayoría de las aplicaciones.

Cada uno de los cuatro resortes mostrados en el esquema de la Figura 2.2 se conforma de una serie de vigas metálicas, cada una de ellas con una rigidez asociada modelada como en la expresión 2.2 de una manera similar a la manera en que opera una viga individual según la Ley de Hooke. A fin de determinar la rigidez k del elemento de longitud L resulta útil aplicar la expresión 2.3 que corresponde a la deflexión de una viga empotrada por un extremo (cantiléver), con módulo de Young E y un momento de inercia I determinados cuando una carga (fuerza) P actúa sobre el extremo libre.

$$F = k\Delta y \tag{2.2}$$

$$k = \frac{F}{\Delta y}$$

$$\Delta y_b = \frac{PL^3}{3EI} \tag{2.3}$$

La Figura 2.3 representa una analogía entre un resorte tradicional (embobinado) y una viga en cantiléver. Debe en este caso, considerarse también el efecto de tener un arreglo de múltiples vigas, conectadas por los extremos para formar un único resorte planar (vigas en serie), así como tener a la masa suspendida por múltiples resortes en paralelo.

De las expresiones 2.2 y 2.3 se puede deducir que la rigidez  $k_b$  de una única viga es tal como en la expresión 2.4, mientras que la ecuación 2.5, es una aproximación a la rigidez total equivalente  $k_s$  de un resorte

Figura 2.3: Equivalencia entre tipos de resortes.

correspondiente a un arreglo de n vigas de longitud L conectadas en serie, despreciando la longitud de las uniones entre vigas por ser mucho menor que L. Se asume también que la longitud de cada viga es muchas veces mayor que su ancho y espesor. La Figura 2.4 presenta resultados de un análisis por elemento finito (FEA) para estimar el desplazamiento de n vigas conectadas en serie ante una fuerza aplicada en su extremo libre, validando así la expresión 2.5.

$$k_b = \frac{3EI}{L^3} \tag{2.4}$$

$$k_{\rm S} \approx \frac{3EI}{nL^3} \tag{2.5}$$

Las ecuaciones 2.6 y 2.7 son respectivamente, la rigidez total equivalente para dos resortes a y b conectados en paralelo y en serie, respectivamente. Como fue visto previamente en la Figura 2.2, los cuatro resortes trabajan en conjunto para alcanzar una rigidez total, tal como se describe en la ecuación 2.8.

$$k_{a||b} = k_a + k_b \tag{2.6}$$

$$k_{a-b} = \frac{k_a k_b}{k_a + k_b}$$

(2.7)

$$k = (k_1 | |k_2) - (k_3 | |k_4)$$

$$k = \frac{(k_1 + k_2)(k_3 + k_4)}{k_1 + k_2 + k_3 + k_4}$$

(2.8)

De las ecuaciones 2.1, 2.3 y 2.8 se desprende una correlación entre la capacitancia C y el desplazamiento  $\Delta y$  de la masa sísmica suspendida por un resorte equivalente de rigidez k, cuya fuerza de restauración se opone a fuerza externas que aceleran al dispositivo.

#### 2.4 Modelo dinámico

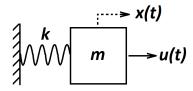

Una expresión general para la dinámica de la masa sísmica y por lo tanto, para la variación de distancia de separación entre terminales del capacitor variable, puede ser deducida a partir de un diagrama de cuerpo libre (tal como el de la Figura 2.5) y la Segunda Ley de Newton. Utilizando la notación usual para sistemas dinámicos, establecemos la expresión 2.9, donde  $\ddot{x}$  describe el desplazamiento acelerado en el eje x de una masa m sobre la cual actúan un estímulo externo u(t) y la fuerza de restitución de un resorte con rigidez k.

$$m\ddot{x} = u(t) - kx$$

$$m\ddot{x} + kx - u(t) = 0 \tag{2.9}$$

Cuando se aplica la Transformada de Laplace a la ecuación 2.9 se obtiene la expresión 2.10 en la que se asumen condiciones iniciales cero, es decir,  $x_0 = 0$  y  $\dot{x}_0 = 0$ . Como es usual, a la relación o razón entre la salida y la entrada de un sistema dinámico se le conoce como Función

Figura 2.4: Validación por FEA del comportamiento de un resorte conformado por n vigas individuales. Desplazamiento proporcional del extremo libre ante una misma fuerza para un número de vigas  $n=1,2\ y\ 4$ .

Figura 2.5: Diagrama de cuerpo libre correspondiente a una masa m y un único resorte con rigidez total equivalente k.

$$-U(s) \longrightarrow \boxed{\frac{1}{m \cdot s^2 + k}} - X(s) \longrightarrow$$

Figura 2.6: Representación en lazo abierto del sistema masa-resorte.