## CENTRO DE INVESTIGACIÓN Y DE ESTUDIOS AVANZADOS DEL INSTITUTO POLITÉCNICO NACIONAL

#### **UNIDAD ZACATENCO**

# DEPARTAMENTO DE INGENIERÍA ELÉCTRICA SECCIÓN DE ELECTRÓNICA DEL ESTADO SÓLIDO

## "SISTEMA DE DESARROLLO DE REDES NEURONALES CELULARES"

TESIS

Que presenta

#### ING. JOSE DE JESUS MORALES ROMERO

Para obtener el grado de

**MAESTRO EN CIENCIAS**

En la especialidad de

INGENIERÍA ELÉCTRICA

Directores de la Tesis: Dr. Felipe Gómez Castañeda Dr. José Antonio Moreno Cadenas

México, D.F.

Noviembre del 2015

## **Agradecimientos**

A CONACYT por el apoyo económico que me otorgo para realizar mi programa de maestría.

A mi familia por todo el apoyo incondicional que me ha brindado durante mis estudios.

A mis asesores Felipe Gómez, José Antonio Moreno por toda su ayuda y apoyo para realizar esta tesis, además de M.C. Luis Martín por su colaboración y consejos, a mis maestros y personal de apoyo.

A mis amigos y compañeros que me han apoyado y dando consejos durante mi programa de maestría.

| Dedicatoria                           |                                       |

|---------------------------------------|---------------------------------------|

|                                       |                                       |

|                                       |                                       |

|                                       |                                       |

|                                       |                                       |

|                                       |                                       |

|                                       |                                       |

| A mi familia, por todo el apoyo que r | ne han otorgado y principalmente a mi |

|                                       | madre por su apoyo incondicional      |

|                                       |                                       |

|                                       |                                       |

## Contenido

| Agradecimi  | ientos                                             | i    |

|-------------|----------------------------------------------------|------|

| Dedicatoria |                                                    | ii   |

| Resumen     |                                                    | viii |

| Introducció | n                                                  | ix   |

| Objetivo    |                                                    | x    |

| Objetivos p | articulares                                        | x    |

| Capítulo 1. | Teoría de Redes Neuronales Celulares               | 1    |

| 1.1 Int     | troducción                                         | 1    |

| 1.2 Ar      | quitectura de la CNN                               | 1    |

| 1.2.1       | Vecindario de una CNN                              | 2    |

| 1.2.2       | Ecuaciones de la CNN                               | 4    |

| 1.2.3       | Función de salida                                  | 5    |

| 1.2.4       | Modelo eléctrico de una neurona                    | 6    |

| 1.2.5       | Condiciones de frontera                            | 7    |

| 1.3 Es      | tabilidad de una CNN                               | 8    |

| 1.4 Pla     | antillas de retroalimentación y control de una CNN | 8    |

| 1.5 Me      | étodos para búsqueda de plantillas                 | 10   |

| 1.6 Ap      | plicaciones de CNN en procesamiento de imágenes    | 12   |

| 1.6.1       | Removedor de Ruido                                 | 12   |

| 1.6.2       | Extractor de bordes para imágenes binarias         | 13   |

| 1.6.3       | Extractor de bordes para imágenes en grises        | 14   |

| 1.6.4       | Extractor de sombras                               | 15   |

| 1.6.5       | Detector de conectividad global                    | 16   |

| 1.7 Co      | onclusiones                                        | 17   |

| 1.8     | Re   | eferencias                                                     | 19      |

|---------|------|----------------------------------------------------------------|---------|

| Capítul | o 2. | Multiplexado en tiempo de una CNN                              | 21      |

| 2.1     | Int  | troducción                                                     | 21      |

| 2.2     | Pa   | sos para multiplexar en tiempo una CNN                         | 21      |

| 2.2     | 2.1  | Obtención de bloques                                           | 22      |

| 2.2     | 2.2  | Orden lexicográfico                                            | 23      |

| 2.3     | Er   | rores en el multiplexado de la CNN                             | 24      |

| 2.3     | 3.1  | Reducción del error                                            | 25      |

| 2.4     | Re   | epetición del tipo de bloques                                  | 27      |

| 2.5     | Al   | goritmo general para el multiplexado en tiempo de una CNN      | 27      |

| 2.6     | Cì   | NN para el multiplexado en tiempo                              | 30      |

| 2.7     | Co   | onclusiones                                                    | 30      |

| 2.8     | Re   | eferencias                                                     | 32      |

| Capítul | o 3. | Descripción de una CNN multiplexada en tiempo con MATLAB y S   | IMULINK |

| 33      |      |                                                                |         |

| 3.1     | Int  | troduccióntroducción                                           | 33      |

| 3.2     | Al   | goritmo de una CNN multiplexada en tiempo                      | 33      |

| 3.3     | Cr   | reación de una CNN de <b>4</b> × <b>4</b> Neuronas en SIMULINK | 34      |

| 3.3     | 3.1  | Integrador Euler                                               | 35      |

| 3.3     | 3.2  | Neurona en SIMULINK                                            | 39      |

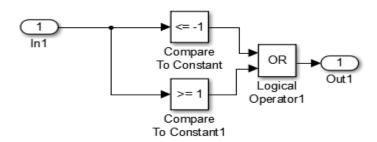

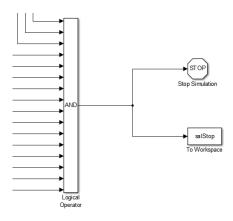

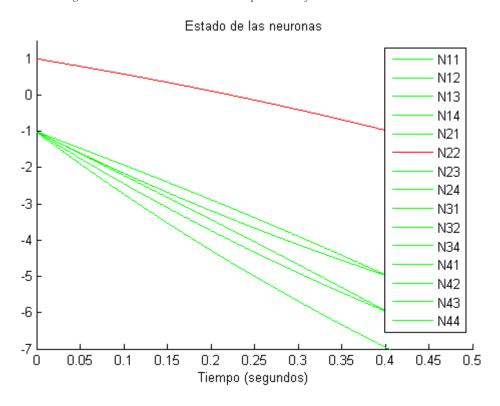

| 3.3     | 3.3  | Comprobación del estado estable                                | 41      |

| 3.3     | 3.4  | Condición de frontera                                          | 42      |

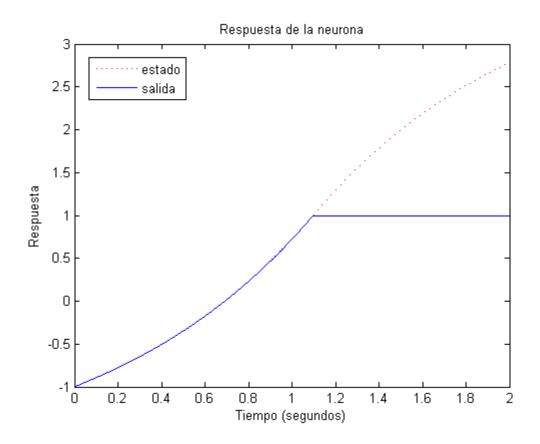

| 3.3     | 3.5  | Prueba de la neurona en SIMULINK                               | 43      |

| 3.3     | 3.6  | Creación de la CNN de <b>4</b> × <b>4</b> Neuronas             | 44      |

| 3.4     | Co   | ontrol de la CNN con MATLAB                                    | 49      |

| 3.4.1      | Proceso "Carga los parámetros"                           | 49 |

|------------|----------------------------------------------------------|----|

| 3.4.2      | Proceso "Calcula la cantidad de bloques"                 | 51 |

| 3.4.3      | Proceso "Obtiene el bloque"                              | 52 |

| 3.4.4      | Proceso "Tipo de bloque"                                 | 53 |

| 3.4.5      | Proceso "Actualiza salida y estados"                     | 54 |

| 3.5 I      | Funcionamiento de la CNN con MATLAB y SIMULINK           | 55 |

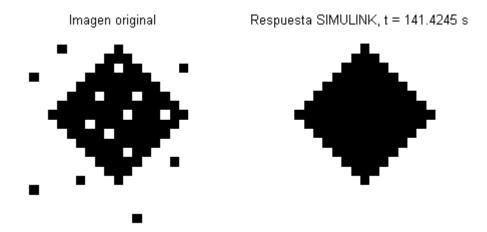

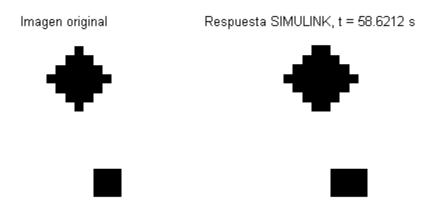

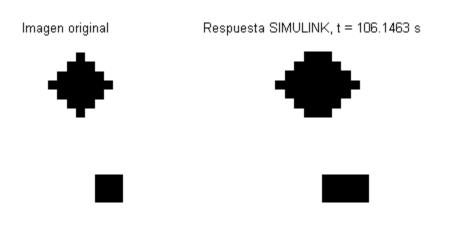

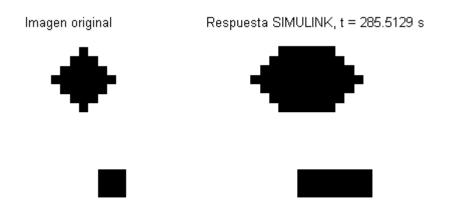

| 3.5.1      | Removedor de ruido                                       | 55 |

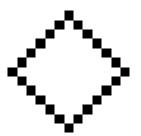

| 3.5.2      | Extractor de Bordes                                      | 55 |

| 3.5.3      | Extractor de sombras                                     | 56 |

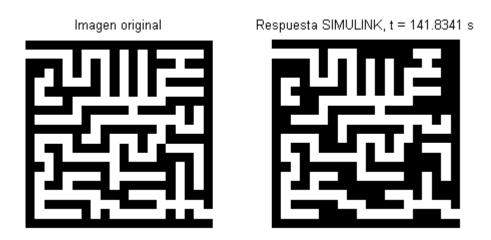

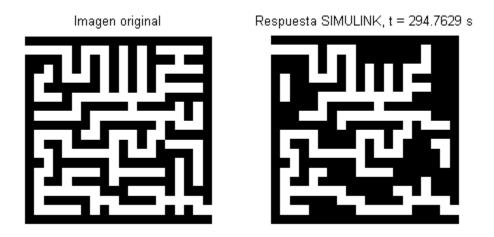

| 3.5.4      | Detector de conectividad global                          | 58 |

| 3.6        | Conclusiones                                             | 59 |

| 3.7 I      | Referencias                                              | 60 |

| Capítulo 4 | 4. Descripción de una CNN multiplexada en tiempo en VHDL | 61 |

| 4.1 I      | Introducción                                             | 61 |

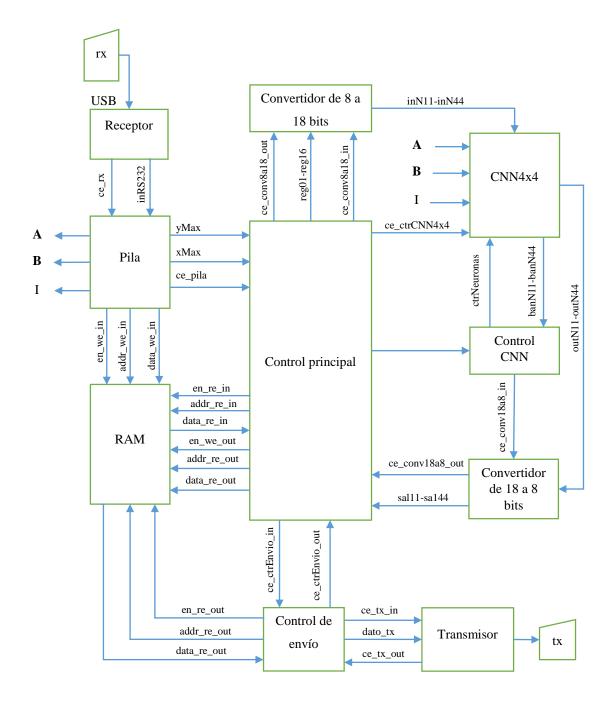

| 4.2 I      | Diagrama a bloques de la CNN                             | 62 |

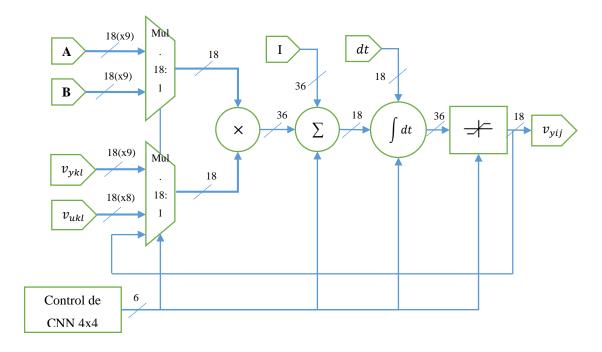

| 4.3 I      | Descripción de una Neurona en VHDL                       | 65 |

| 4.4 I      | Descripción de la CNN 4x4 en VHDL                        | 67 |

| 4.5 N      | Multiplexado de la CNN en VHDL                           | 68 |

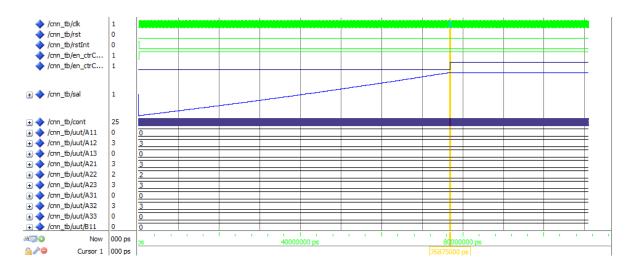

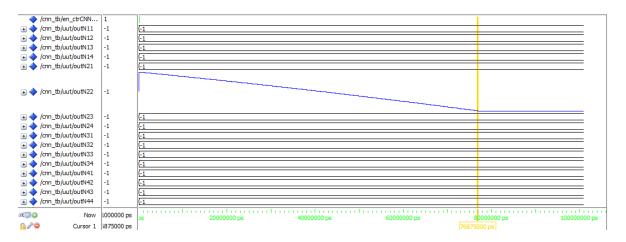

| 4.6 I      | Prueba de la CNN                                         | 70 |

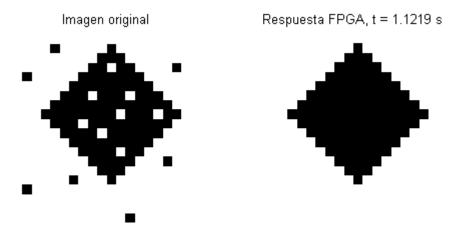

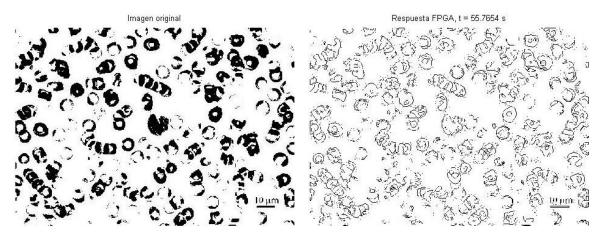

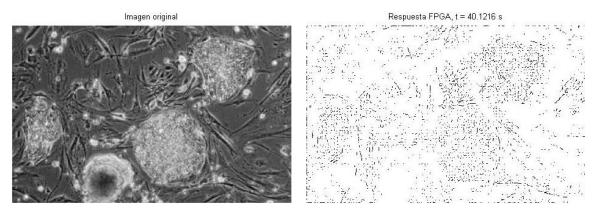

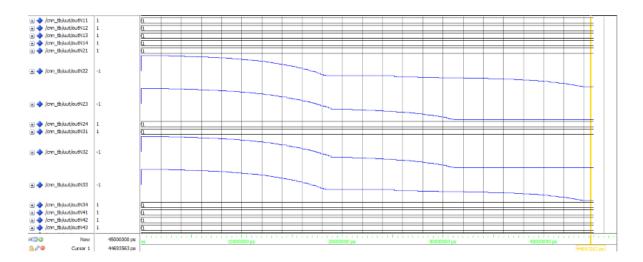

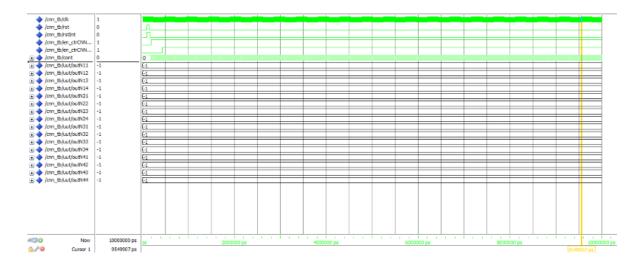

| 4.6.1      | Removedor de ruido                                       | 71 |

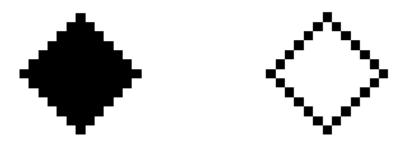

| 4.6.2      | Extractor de bordes                                      | 72 |

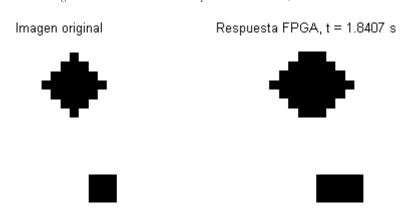

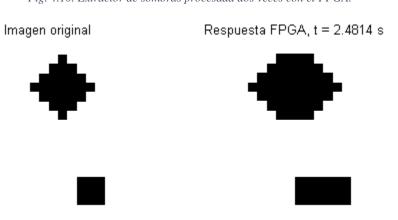

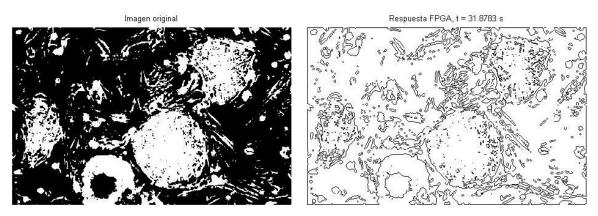

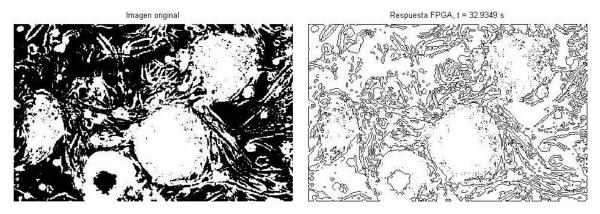

| 4.6.3      | Extractor de sombras                                     | 72 |

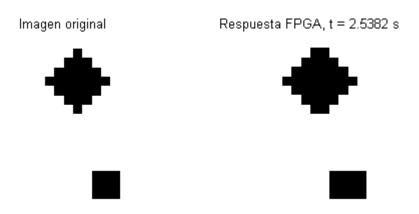

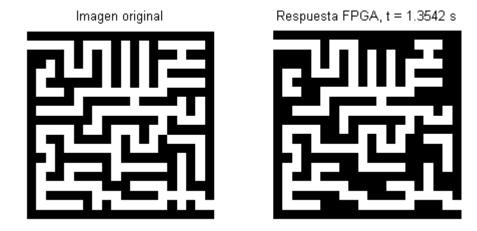

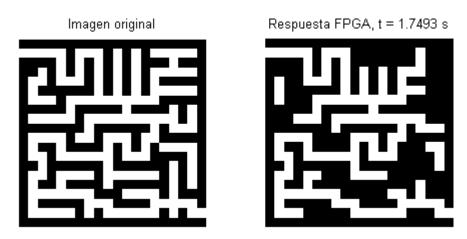

| 4.6.4      | Detector de conectividad global                          | 74 |

| 4.7        | Conclusiones                                             | 75 |

| 4.8 I      | Referencias                                              | 76 |

| Resultados                                            | 77  |

|-------------------------------------------------------|-----|

| Conclusiones                                          | 89  |

| Trabajo futuro                                        | 91  |

| Apéndice                                              | 92  |

| A. Código en MATLAB para el multiplexado de una CNN.  | 92  |

| B. Código en VHDL para el multiplexado de una CNN.    | 98  |

| C. Código en MATLAB para la comunicación con el FPGA. | 125 |

#### **Preface**

Since Cellular Neural Networks were introduced, there have been several studies about these, such as search templates, numerical integration methods to solve the state equation of each of the neurons in the network, and these networks have been used to solve problems such as the image processing. However, it notes that these solutions lead to a large consumption of resources, which is why this paper has proposed a method of reducing the resources needed to perform well CNN and process very large images. The method introduced in this paper is multiplexing CNN.

In Chapter 1, we talk mainly about the theory of Cellular Neural Networks. In this chapter we talk about architecture and stability of CNN also we will explain what are the templates and existing methods for searching the templates, as these define what CNN will do. Finally, some examples of use of Cellular Neural Network are given as image processor. In Chapter 2, we talk mainly about the theory of multiplexing of CNN and its characteristics and general algorithm, along with their advantages and disadvantages. In addition, we will talk about the conditions that must be met for CNN multiplexing is performed correctly.

In chapter 3, we talk about the simulator that has been done on MATLAB and Simulink, which performs multiplexing of our CNN, to verify the correct operation that has this so that it can be physically implemented. The proper functioning of the simulator performing basic image processing will be verified. In Chapter 4, the most important part of our work will be done, which is the physical realization of our multiplex CNN for image processing. We will talk about how it was developed using VHDL to describe the circuit to be implemented within the FPGA. In addition, proper operation performing basic image processing is checked.

Finally, in the section "Results" of this paper some examples of processing real images using our implementation with FPGA, along with some recommendations and limitations of our implementation are given.

#### Resumen

Desde que las Redes Neuronales Celulares fueron introducidas, se han realizado diversos estudios a cerca de estas, como por ejemplo la búsqueda de plantillas, métodos de integración numérica que resuelvan la ecuación de estado de cada una de las neuronas dentro de la red, así como se han utilizado estas redes para la solución de problemas como lo es el procesamiento de imágenes. Sin embargo, cabe destacar que estas soluciones conllevan a un consumo muy grande de recursos, es por esto que este trabajo se ha propuesto un método de reducir los recursos necesarios para realizar la CNN y así procesar imágenes muy grandes. El método introducido en este trabajo consiste en la multiplexación de la CNN.

En el capítulo 1 se habla principalmente sobre la teoría de las Redes Neuronales Celulares. Dentro de este capítulo se hablara sobre la arquitectura y la estabilidad de una CNN, además se explicará lo que son las plantillas y los métodos que existen para la búsqueda de las plantillas, ya que estas definen lo que realizarla la CNN. Finalmente, se dan algunos ejemplos del uso de la Red Neuronal Celular como procesador de imágenes. En el capítulo 2, se habla principalmente sobre la teoría del multiplexado de una CNN, así como sus características y su algoritmo general, además de sus ventajas y desventajas. Además, se hablará sobre las condiciones que se deben de cumplir para que el multiplexado de la CNN se realice de forma correcta.

En el capítulo 3, se habla sobre el simulador que se ha realizado sobre MATLAB y SIMULINK, que realiza el multiplexado de nuestra CNN, para verificar el correcto funcionamiento que tiene esta y poderlo así implementar físicamente. Se verificará el correcto funcionamiento del simulador realizando procesamiento de imágenes básicas. En el capítulo 4 se realizará la parte más importante de nuestro trabajo, lo cual es la realización física de nuestra CNN multiplexada para el procesamiento de imágenes. Se hablará de cómo fue desarrollada utilizando VHDL para describir el circuito que será implementado dentro del FPGA. Además, se comprobará su correcto funcionamiento realizando el procesamiento de imágenes básicas.

Finalmente, en la parte de "Resultados" de este trabajo se dan algunos ejemplos del procesamiento de imágenes reales utilizando nuestra implementación con el FPGA, además de algunas recomendaciones y limitaciones que tiene nuestra implementación.

#### Introducción

En la actualidad, el campo de la electrónica ha estado creciendo en forma exponencial y un ejemplo de esto es el desarrollo de los procesadores digitales; estos procesadores tienen grandes capacidades de procesamiento y velocidades muy altas, sin embargo, éstos aún no pueden resolver varios problemas de forma óptima y rápida, como lo es el procesamiento de imágenes y video, reconocimiento de patrones, resolución de ecuaciones diferenciales, entre otras, debido a su naturaleza de procesamiento serial que poseen este tipo de procesadores. Es por esto que se han propuesto varias alternativas para solucionar esta problemática como lo son las Redes Neuronales Celulares que poseen una gran capacidad de procesamiento paralelo.

Desde que L. O. Chua y L. Yang presentaran las Redes Neuronales Celulares en el año de 1988, se han realizado diversos estudios acerca de éstas. Algunos de estos estudios incluyen como por ejemplo, la optimización y búsqueda de plantillas robustas para el procesamiento de diferentes tareas, otros estudios realizan una comparativa sobre los diversos métodos de integración numérica que resuelvan la ecuación de estado dentro de las Redes Neuronales Celulares, también se han realizado estudios sobre la resolución de problemas en el campo de la visión y el procesamiento de imágenes.

Dentro de estos estudios se presenta el procesamiento de imágenes, sin embargo, debido a que como veremos más adelante, la CNN utilizada debe de ser del mismo tamaño que la imagen a ser procesada. Debido a lo anterior, se han realizado propuestas como lo es el multiplexado de la CNN, esto quiere decir, que se van procesando fracciones de la imagen original dentro de la CNN, esto hasta completar la imagen. Esta propuesta resulta atractiva debido a que con esta técnica se reducen los recursos necesarios que se requieren para el procesamiento de imágenes.

## Objetivo

El objetivo de este trabajo es presentar el desarrollo de una CNN digital de 4 × 4 neuronas la cual será implementada físicamente en un FPGA, sin embargo esta CNN, a diferencia de otras CNN's presentadas en diversos trabajos, tendrá la capacidad de ser multiplexada. Además se desarrollará un simulador de CNN igualmente de 4 × 4 neuronas, el cual será implementado dentro del programa MATLAB utilizando SIMULINK para el procesamiento paralelo de las neuronas. El objetivo de realizar esta implementación y simulador es debido a que actualmente las CNN's se han ido desarrollando e investigado sus características y formas de optimización, y dentro de estas investigaciones se encuentra el procesamiento de imágenes, con lo cual nuestra CNN desarrollada se utilizará principalmente para diferentes tipos de procesamiento de imágenes de cualquier tamaño, además de que ésta será capaz de realizar procesamiento de imágenes en escala de grises y no únicamente de imágenes en escala de blancos y negros, como ocurre en otros trabajos realizados previamente.

## **Objetivos particulares**

Los objetivos particulares de este trabajo son primero el aprendizaje sobre la teoría de las CNN's, así como sus ventajas y desventajas del uso de las CNN's para la resolución de problemas, segundo el desarrollo de un simulador CNN multiplexado para comprobar el comportamiento de esta, y finalmente el desarrollo de una CNN dentro de un FPGA para realizar procesamiento de imágenes.

#### Capítulo 1. Teoría de Redes Neuronales Celulares

#### 1.1 Introducción

Hoy en día diversas aplicaciones de la electrónica como lo son en el campo de la computación, almacenamiento de datos, comunicaciones, control, procesamiento de imágenes, reconocimiento de patrones, video, etc., podrían ser resueltas por procesadores digitales que trabajan en forma serial, sin embargo, hay aplicaciones donde este tipo de procesadores están limitados, como son el reconocimiento de patrones, el procesamiento de imágenes y video, procesamiento no lineal en general y solución de ecuaciones diferenciales, entre otras. Para resolver este tipo de problemas, se han propuesto varias alternativas de solución como son los circuitos integrados CNN, autómatas celulares, retinas de silicio, circuitos integrados de aplicación específica (ASICs), entre otros.

Las Redes Neuronales Celulares (CNN por sus siglas en inglés "Cellular Neural Networks") fueron introducidas por L. O. Chua y L. Yang en el año de 1988. Las Redes Neuronales Celulares poseen características de procesamiento paralelo de las Redes Neuronales y la interconexión de los Autómatas Celulares; en las primeras, éstas se caracterizan porque pueden ser integradas tecnológicamente como un circuito analógico no lineal que son capaces de procesar señales en tiempo real y en las segundas porque pueden ser identificadas como un arreglo de elementos regulares analógicos [1].

La CNN está compuesta de unidades básicas que están interconectadas entre sí en forma de arreglo teniendo así características como el procesamiento paralelo, dinámica en tiempo continuo e interacción global entre los elementos de la red.

#### 1.2 Arquitectura de la CNN

Como se mencionó anteriormente, las CNN son arreglos de elementos básicos, estos elementos son llamados *celdas* o *neuronas*, estas *neuronas* están compuestas de elementos eléctricos como resistencias, capacitores y fuentes de corriente controladas por voltaje y fuentes independientes de voltaje [1] [2]. La interconexión de las *neuronas* es similar a las encontradas en los autómatas celulares. Esto es, que una neurona dentro de una CNN está conectada a las neuronas vecinas. Las neuronas que se encuentran adyacentes entre sí pueden

interactuar directamente entre ellas y las neuronas que no están conectadas directamente pueden afectarse indirectamente entre ellas debido a los efectos de propagación de la dinámica en tiempo continuo de la CNN [1] y [3].

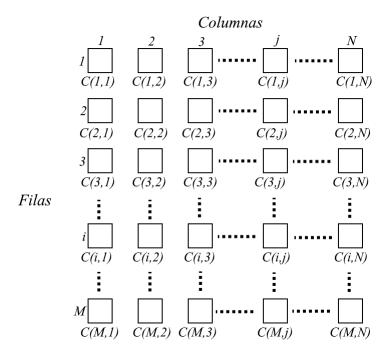

Teóricamente una CNN puede ser de diversas dimensiones como es mostrado en los trabajos [1], [2] y [4], sin embargo, es más frecuente encontrar CNN's de dos dimensiones. Una arquitectura estándar de una CNN, como la mostrada en la Fig. 1.1, está compuesta de un arreglo rectangular de MN neuronas (C(i,j)) donde M es la cantidad de filas, N la cantidad de columnas, e (i,j) son las coordenadas cartesianas correspondientes a la posición de la neurona [2] y [3].

Fig. 1.1 Estructura básica de una CNN

#### 1.2.1 Vecindario de una CNN

El vecindario  $N_r(i,j)$  o esfera de influencia de radio r en una neurona C(i,j) dentro de una CNN está definido como el conjunto de todas las neuronas del vecindario que satisfacen la siguiente propiedad [1] y [2]:

$$N_r(i,j) = \{C(k,l) | \max\{|k-i|, |l-j|\} \le r, 1 \le k \le M; 1 \le l \le N\}$$

(1.1)

Donde r es un entero positivo.

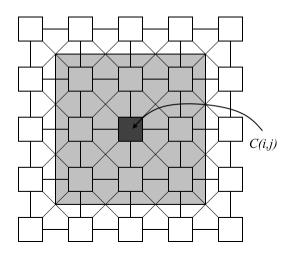

Algunas veces nos referiremos al vecindario  $N_r(i,j)$  como un vecindario de  $\left((2r+1)\times(2r+1)\right)$  neuronas para el caso de una CNN de dos dimensiones [1] y [2]. En la Fig. 1.2 observamos un vecindario de r=1 o también llamado un vecindario de  $(3\times3)$  neuronas.

Fig. 1.2 CNN con r = 1, (vecindario de (3x3) neuronas)

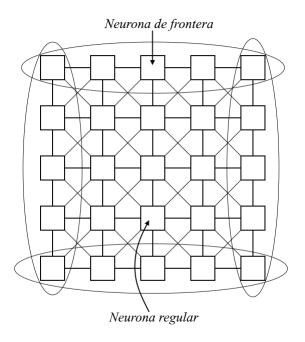

Se llama *neurona regular* si y solo si todas las neuronas dentro del vecindario  $N_r$  existen, de otra forma se les llama *neuronas de frontera*; esto es mostrado en la Fig. 1.3.

Fig. 1.3. Tipos de neurona.

Cuando r > N/2 y M = N, tenemos una CNN totalmente conectada, donde cada neurona está conectada a cada una de las demás neuronas y  $N_r(i,j)$  es toda la matriz. Este caso extremo corresponde a la clásica red de Hopfield [2].

#### 1.2.2 Ecuaciones de la CNN

La dinámica de una neurona C(i, j) en la CNN está definida por la siguiente *ecuación* de estado [1] y [2]:

$$C\frac{dv_{xij}(t)}{dt} = -\frac{1}{R_x}v_{xij}(t) + \sum_{C(k,l)\in N_r(i,j)} A(i,j;k,l)v_{ykl}(t) + \sum_{C(k,l)\in N_r(i,j)} B(i,j;k,l)v_{ukl} + I_{ij}$$

(1.2)

Donde  $1 \le i \le M$  y  $1 \le j \le N$ .

Haciendo C=1 y  $R_x=1$  en la ecuación (1.2), obtenemos la ecuación normalizada de estado:

$$\frac{dv_{xij}(t)}{dt} = -v_{xij}(t) + \sum_{C(k,l) \in N_T(i,j)} A(i,j;k,l)v_{ykl}(t) + \sum_{C(k,l) \in N_T(i,j)} B(i,j;k,l)v_{ukl} + I_{ij}$$

(1.3)

Donde  $v_{xij}$  es el estado de la neurona C(i,j) y su condición inicial es asumida para tener una magnitud menor o igual a 1,  $v_{uij}$  es la entrada de la neurona C(i,j), y es asumida para ser una constante con magnitud menor o igual a 1,  $v_{ukl}$  son las estradas de las neuronas vecinas,  $v_{yij}$  es la salida de la neurona C(i,j),  $v_{ykl}$  son las salidas de las neuronas vecinas e I es el umbral, A(i,j;k,l) es llamada plantilla de retroalimentación y B(i,j;k,l) es llamada plantilla de control, (i,j) indican el índice de la neurona actual y (k,l) indican los índices vecinales de la red neuronal.

#### 1.2.3 Función de salida

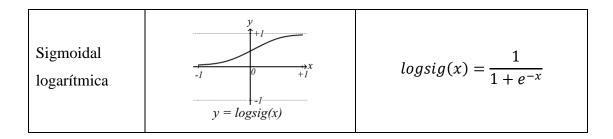

Además, se establece la función de salida, que es la única función no lineal dentro de la neurona. Existen varias funciones de salida utilizadas, algunas de estas funciones se muestran en la siguiente tabla:

Tabla 1.1. Funciones de transferencia en redes neuronales

| Función                              | Símbolo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Definición                                                                                              |

|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|

| Lineal                               | y = y $y = y$ $y =$ | purelin(x) = x                                                                                          |

| Saturación<br>lineal positiva        | $y = \int_{-1}^{y} \frac{1}{y} dx$ $y = satlin(x)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | $satlin(x)$ $= \begin{cases} 0, & si \ x \le 0 \\ x, & si \ 0 < x < 1 \\ 1, & si \ x \ge 1 \end{cases}$ |

| Signo                                | y $-1$ $0$ $+1$ $y = hardlims(x)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | $hardlims(x)$ $= \begin{cases} -1, & \text{si } x < 0 \\ 1, & \text{si } x \ge 0 \end{cases}$           |

| Signo positiva                       | $y$ $\downarrow^{-1}$ $0$ $+1$ $y = hardlim(x)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | $harlim(x) = \begin{cases} 0, & si \ x < 0 \\ 1, & si \ x \ge 0 \end{cases}$                            |

| Sigmoidal<br>tangente<br>hiperbólica | y = tansig(x)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | $tansig(x) = \frac{2}{1 + e^{-2x}} - 1$                                                                 |

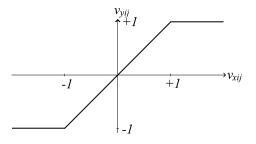

Sin embargo, la función de salida más utilizada para el procesamiento de imágenes es la función de transferencia "Saturación Lineal Simétrica", que es representada por la siguiente ecuación:

$$v_{yij}(t) = \frac{1}{2} (|v_{xij}(t) + 1| - |v_{xij}(t) - 1|)$$

(1.4)

En la Fig. 1.4 se muestra la gráfica de la función de salida, que es la función de transferencia de "Saturación Lineal Simétrica", donde para el procesamiento de imágenes se tiene que si  $v_{yij} = 1$  correspondiente a un pixel negro y para  $v_{yij} = -1$  corresponde a un pixel blanco.

Fig. 1.4 Función de transferencia "Saturación Lineal Simétrica"

#### 1.2.4 Modelo eléctrico de una neurona

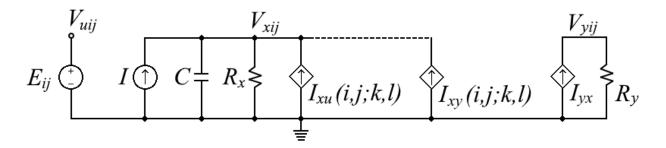

El modelo eléctrico típico de una neurona es mostrado en la siguiente figura, donde u representa la entrada, x el estado e y representa la salida, donde este modelo de neurona sigue la ecuación (1.2).

Fig. 1.5. Modelo eléctrico de una neurona en la CNN

El voltaje en el nodo  $v_{xij}$  representa el estado de la neurona, el voltaje en el nodo  $v_{uij}$  representa la entrada de la neurona, y el voltaje en el nodo  $v_{yij}$  representa la salida. Las fuentes  $I_{xy}(i,j;k,l)$  e  $I_{xu}(i,j;k,l)$  son fuentes de corriente controladas por voltaje que tienen las características de la ecuación (1.2) donde representan:

$$I_{xy}(i,j;k,l) = A(i,j;k,l)v_{ykl}$$

(1.5)

$$I_{ru}(i,j;k,l) = B(i,j;k,l)v_{ukl}$$

(1.6)

Como se mencionó anteriormente, el único elemento no lineal es la función de transferencia "Saturación Lineal Simétrica" que es representada por la fuente de corriente controlada por voltaje  $I_{yx} = \binom{1}{R_y} v_{xij}$  donde observamos que depende del estado de la neurona  $v_{xij}$ .

#### 1.2.5 Condiciones de frontera

Como se mencionó en 1.2.1 existen la neurona regular y la neurona de frontera. Para este último caso las neuronas deben de cumplir las condiciones de frontera para su correcto funcionamiento, para esto existen tres de condiciones de frontera que son las más utilizadas [2] dentro de las CNN, las cuales se mencionan a continuación:

1. Condición de frontera fija (Dirichlet): En este tipo de frontera los valores de las variables de estado  $v_{xkj}$  y salida  $v_{ykl}$  de las neuronas de frontera están asignados a un valor constante, generalmente 0.

- 2. Condición de frontera de flujo cero (Neumann): En este tipo de frontera los valores de las variables de estado y la salida son iguales a los valores de las neuronas adyacentes.

- 3. *Condición de frontera periódica (Toroidal)*: En este tipo de frontera los valores de las variables de estado y la salida son iguales a los valores de las neuronas que se encuentran en el otro extremo de la CNN.

#### 1.3 Estabilidad de una CNN

La función básica de una CNN para el procesamiento de imágenes es transformar una imagen de entrada en su respectiva imagen de salida, para ello cada pixel de una imagen será procesada por una neurona. Con lo cual aquí se restringen los valores de salida a [-1,1]. Sin embargo, las entradas de los pixeles pueden contener diversos niveles de grises con lo cual se restringen estas entradas a:

$$|v_{uij}| \le 1, \quad 1 \le i \le M, 1 \le j \le N$$

(1.7)

Como se demuestra en el trabajo realizado por L. O. Chua y L. Yang [1], se tiene que para que no oscile la red se debe de cumplir que:

$$A(i,j;i,j) > 1 \tag{1.8}$$

Con esto también se garantiza que la salida de la neurona será binaria.

#### 1.4 Plantillas de retroalimentación y control de una CNN

En el caso de una CNN con vecindario r=1 y considerando parámetros invariantes, las plantillas de retroalimentación (plantilla  $\boldsymbol{A}$ ), control (plantilla  $\boldsymbol{B}$ ) y el umbral (I) se pueden representar de la siguiente manera:

$$\mathbf{A} = \begin{bmatrix} a_{i-1,j-1} & a_{i-1,j} & a_{i-1,j+1} \\ a_{i,j-1} & a_{i,j} & a_{i,j+1} \\ a_{i+1,j-1} & a_{i+1,j} & a_{i+1,j+1} \end{bmatrix}, \mathbf{B} = \begin{bmatrix} b_{i-1,j-1} & b_{i-1,j} & b_{i-1,j+1} \\ b_{i,j-1} & b_{i,j} & b_{i,j+1} \\ b_{i+1,j-1} & b_{i+1,j} & b_{i+1,j+1} \end{bmatrix}, I_{i,j}$$

(I.9)

Ahora considere una neurona típica C(i,j) dentro del vecindario  $N_r(i,j)$  como sigue:

| C(i-1,j-1) | C(i-1,j) | C(i-1,j+1) |

|------------|----------|------------|

| C(i,j-1)   | C(i,j)   | C(i, j+1)  |

| C(i+1,j-1) | C(i+1,j) | C(i+1,j+1) |

Podemos así escribir para el caso de la plantilla A:

$$\sum_{C(k,l)\in N_{r}(i,j)}A(i,j;k,l)y_{kl}=\sum_{|k-i|\leq 1}\sum_{|l-j|\leq 1}A(k-i,l-j)y_{kl}$$

$$= a_{-1,-1}y_{i-1,j-1} + a_{-1,0}y_{i-1,j} + a_{-1,1}y_{i-1,j+1} + a_{0,-1}y_{i,j-1} + a_{0,0}y_{i,j}$$

$$+ a_{0,1}y_{i,j+1} + a_{1,-1}y_{i+1,j-1} + a_{1,0}y_{i+1,j} + a_{1,1}y_{i+1,j+1}$$

$$(1.10)$$

$$= \sum_{k=-1}^{1} \sum_{l=-1}^{1} a_{k,l} y_{l+k,j+l}$$

De esta forma podemos reescribir la ecuación anterior como:

Donde el símbolo \* representa la suma de los productos punto. En matemáticas discretas esta operación es llamada "convolución espacial" [2].

De la misma forma podemos hacer el análisis para la plantilla **B**:

$$\sum_{C(k,l)\in N_{r}(i,j)} B(i,j;k,l)u_{kl} = \sum_{|k-i|\leq 1} \sum_{|l-j|\leq 1} B(k-i,l-j)u_{kl}$$

$$= b_{-1,-1}u_{i-1,j-1} + b_{-1,0}u_{i-1,j} + b_{-1,1}u_{i-1,j+1} + b_{0,-1}u_{i,j-1} + b_{0,0}u_{i,j}$$

$$+ b_{0,1}u_{i,j+1} + b_{1,-1}u_{i+1,j-1} + b_{1,0}u_{i+1,j} + b_{1,1}u_{i+1,j+1}$$

$$= \sum_{k=-1}^{1} \sum_{l=-1}^{1} b_{k,l}u_{i+k,j+l}$$

(1.12)

Escribiendo la ecuación anterior como:

#### 1.5 Métodos para búsqueda de plantillas

Las plantillas A y B, junto con el valor de umbral I y el estado inicial  $v_{xij}(0)$ , determinan el tipo de procesamiento que realizará la CNN; a diferencia de otras estructuras neuronales, no existe un método único para encontrar dichos parámetros [5] y [6].

Los métodos para encontrar los valores de los parámetros de la CNN se pueden agrupar como: *métodos analíticos* [7] - [10], estos métodos se basan en una serie de reglas locales que caracterizan la dinámica de la neurona dentro de la CNN. Para realizar esto, se forma un conjunto de desigualdades que deben ser resueltas mediante un método de optimización; *algoritmos de aprendizaje local* [11]-[15], estos algoritmos se basan en los algoritmos de entrenamiento de otras Redes Neuronales, estos algoritmos pueden ser "recurrent backpropagation", "backpropagation through time" y el aprendizaje de "perceptron"; algoritmos de aprendizaje global [16] y [17], similar a los algoritmos de aprendizaje local, los cuales presentan pares de datos de entrada-salida, donde estos datos son presentados de manera global a toda la CNN y no solamente a la neurona de forma local. Como vemos, en estos algoritmos su nivel de dificultad se va incrementando debido al incremento de número de variable, además esto produce que se presenten dificultades para encontrar la solución de las ecuaciones desarrolladas.

Los *métodos heurísticos* han sido desarrollados para cubrir los problemas de los métodos anteriormente mencionados. La búsqueda de plantillas ha sido tratado como un importante estudio de optimización y por lo tanto, muchos métodos basados en *Inteligencia Artificial* han sido propuestos como lo son: Optimización de Nube de Partículas también llamado *PSO* (por sus siglas en inglés de *Particle Swarm Optimization*), Algoritmos Genéticos también llamado *GA* (por sus siglas en inglés de *Genetic Algorithm*), Evolución Diferencia también llamado *DE* (por sus siglas en inglés de *Differential Evolution*), etc.

Algunos de los métodos para la búsqueda numérica de plantillas son presentados a continuación:

**Método simplex**: Este método fue propuesto por Koji Nakai y Akio Ushida en el año de 1995 [18]. Este método de búsqueda de plantillas se basa en forzar la salida dependiendo de un determinado patrón de entrada, con esto se crean diversas desigualdades y finalmente con éstas, crear una función objetivo.

Establecida la función objetivo se procede a buscar la solución óptima utilizando el método simplex, el cual tiene la ventaja de no utilizar derivadas en su algoritmo, sin embargo, este método no es tan eficiente como los algoritmos que usan derivadas, además de que conforme va incrementado el número de variables de la función objetivo, no se llega a un resultado óptimo.

El algoritmo simplex crea una serie de puntos alrededor de un punto inicial (estos puntos se crean haciendo una reflexión, una expansión y una contracción) de una función objetivo con dimensión n, donde el peor punto es sustituido iterativamente hasta encontrar la convergencia de la función objetivo.

En el trabajo realizado en [5] se muestra el uso de este método para encontrar las plantillas.

**Método ABC**: El algoritmo "Colonia de Abejas Artificial" también llamado ABC (por sus siglas en inglés de "Artificial Bee Colony") es un algoritmo basado en el comportamiento de búsqueda de alimento de las abejas, este tipo de algoritmo pertenece a los llamados algoritmos bio-inspirados.

En el trabajo realizado en [6] se utiliza este tipo de algoritmo para búsqueda de plantillas. Este algoritmo fue en un principio desarrollado por Dervis Karaboga en 2005. Como se mencionó anteriormente, este algoritmo se basa en la búsqueda de alimento por parte de las abejas, donde existen tres tipos de abejas: las abejas trabajadoras, las abejas observadoras y las abejas exploradoras. En un principio, las abejas exploradoras son enviadas a la búsqueda de fuentes de alimento, después las abejas observadoras son enviadas a las fuentes de alimento que encontraron las abejas exploradoras y calculan la cantidad de alimento encontrado, en una tercera fase se asegura que las abejas exploradoras busquen

nuevo alimento aleatoriamente cercano al alimento encontrado anteriormente; aquí la cantidad de alimento representa la solución buscada.

#### 1.6 Aplicaciones de CNN en procesamiento de imágenes

Una de las aplicaciones de las CNN es en el procesamiento de imágenes debido a su característica de procesamiento paralelo. A continuación se mostrarán algunos ejemplos en el procesamiento de imágenes con CNN.

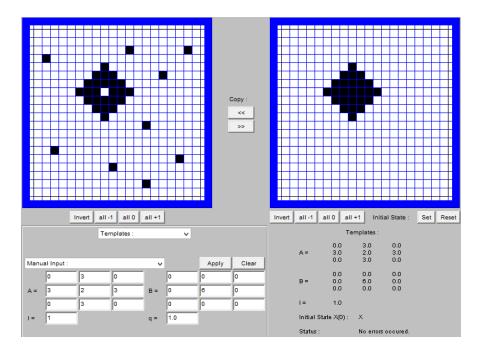

Para comprobar la respuesta de la CNN se utilizará un simulador creado por Simón Moser and Eric Pfaffhauser del Instituto de Procesamiento de Información y Señales de Zúrich, cuya versión es 2.1 y cuya última revisión se realizó en Diciembre de 1998, con dirección electrónica: <a href="http://www.isiweb.ee.ethz.ch/haenggi/CNN\_web/CNNsim\_adv.html">http://www.isiweb.ee.ethz.ch/haenggi/CNN\_web/CNNsim\_adv.html</a>

#### 1.6.1 Removedor de Ruido

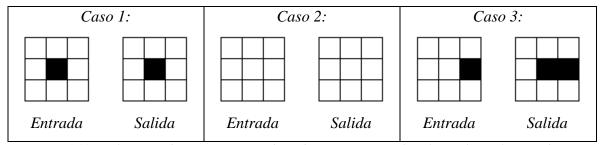

Este proceso radica en recuperar una imagen cuando existe ruido en ella; se considerará ruido cuando un pixel tenga un color diferente al de sus vecinos verticales u horizontales, estos se muestran en la siguiente figura:

Fig. 1.6. Pixeles que son considerados como ruido, en ambos casos el pixel del centro es el considerado ruido.

Para ejemplificar el removedor de ruido, se utilizarán las siguientes plantillas y valor de umbral, los cuales son tomados de [18]:

$$A = \begin{bmatrix} 0 & 3 & 0 \\ 3 & 2 & 3 \\ 0 & 3 & 0 \end{bmatrix}, B = \begin{bmatrix} 0 & 0 & 0 \\ 0 & 6 & 0 \\ 0 & 0 & 0 \end{bmatrix}, I = 1.0$$

Con lo cual obtenemos la siguiente respuesta en el simulador antes mencionado:

Fig. 1.7. Ejemplo Removedor de Ruido

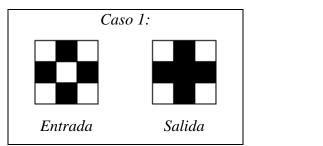

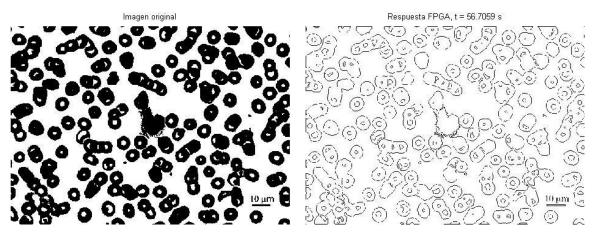

#### 1.6.2 Extractor de bordes para imágenes binarias

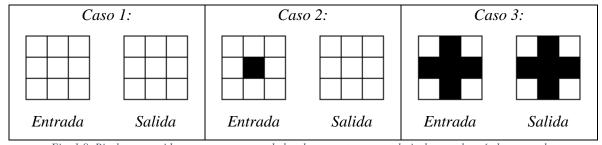

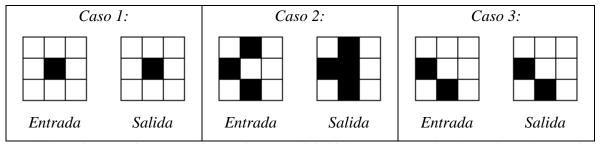

La obtención de bordes es importante ya que permite reducir la cantidad de información de la imagen y solo quedarse con la información más esencial de la imagen; las consideraciones para este ejemplo son las siguientes: Si un pixel es de color blanco su salida debe de ser blanco, si un pixel es de color negro y todos sus vecinos son de color blanco su salida debe de ser blanco de otro modo la salida es de color negro; éstos se ejemplifican en la siguiente figura.

Fig. 1.8. Pixeles a considerar para extractor de bordes, en estos casos el pixel central será el procesado.

Para ejemplificar el uso de la CNN en el extractor de bordes, se utilizan las siguientes plantillas y valor de umbral, estos valores son tomados de [5]:

$$A = \begin{bmatrix} 0 & 0 & 0 \\ 0 & 4 & 0 \\ 0 & 0 & 0 \end{bmatrix}, B = \begin{bmatrix} 0 & -2 & 0 \\ -2 & 5 & -2 \\ 0 & -2 & 0 \end{bmatrix}, I = -1.0$$

Con lo cual obtenemos la siguiente respuesta:

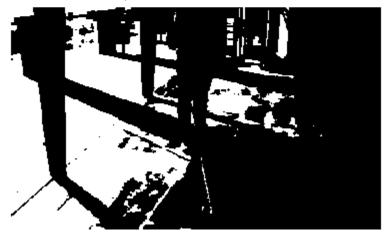

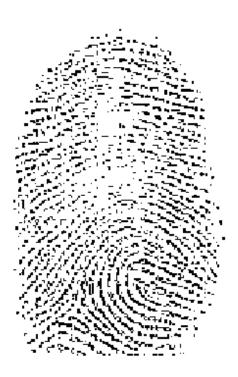

Fig. 1.9. Ejemplo Extractor de bordes

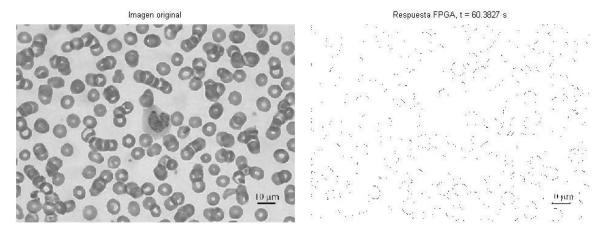

#### 1.6.3 Extractor de bordes para imágenes en grises

Parecido al anterior, sin embargo, en esta ocasión se procesan imágenes en escala de grises, lo cual significa que los valores de entrada ya no solo serán 1's o -1's sino tendrán valores intermedios, para esto se utilizarán las siguientes plantillas, estos valores son tomados de [2].

$$A = \begin{bmatrix} 0 & 0 & 0 \\ 0 & 2 & 0 \\ 0 & 0 & 0 \end{bmatrix}, B = \begin{bmatrix} -1 & -1 & -1 \\ -1 & 8 & -1 \\ -1 & -1 & -1 \end{bmatrix}, I = -0.5$$

Cuya respuesta es la siguiente:

Fig. 1.10. Ejemplo Extractor de Bordes para imágenes en escala de Grises

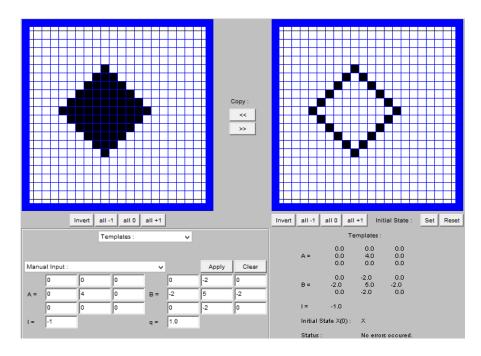

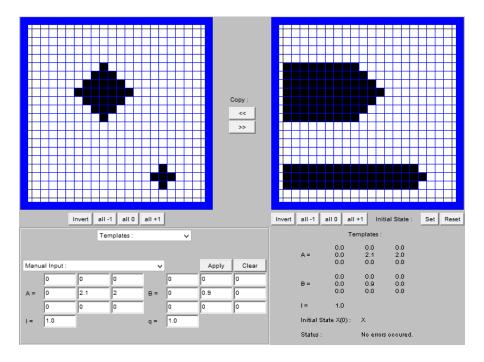

#### 1.6.4 Extractor de sombras

En este procesamiento se hace una proyección de la imagen, en este caso hacia la izquierda; para este ejemplo se hacen las siguientes consideraciones: si un pixel es negro su salida siempre será negro, si un pixel es blanco y el pixel a la derecha es blanco su salida será en blanco y finalmente si un pixel es blanco y el pixel a la derecha es color negro su salida será negro, esto se ejemplifica en la siguiente figura.

Fig. 1.11. Pixeles a considerar para extractor de sombra, en estos casos el pixel central será el procesado.

Para realizar esto se utilizarán las siguientes plantillas y valor de umbral, los cuales son obtenidos de [5]:

$$A = \begin{bmatrix} 0 & 0 & 0 \\ 0 & 2.1 & 2 \\ 0 & 0 & 0 \end{bmatrix}, B = \begin{bmatrix} 0 & 0 & 0 \\ 0 & 0.9 & 0 \\ 0 & 0 & 0 \end{bmatrix}, I = 1.0$$

Con lo cual obtenemos la siguiente respuesta:

Fig. 1.12. Ejemplo Extractor de Sombras

En este ejemplo hay que hacer una aclaración: la proyección de sombra dependerá del tiempo de procesamiento de la CNN, así conforme avance el tiempo se irá expandiendo la sombra en la CNN, sin embargo, para este trabajo se ha determinado que se detenga la simulación hasta llegar a un punto de saturación.

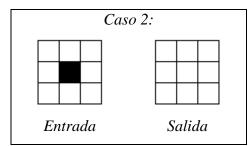

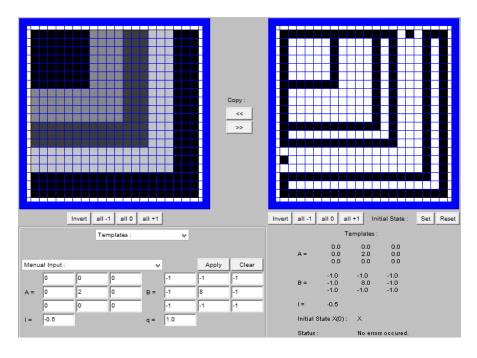

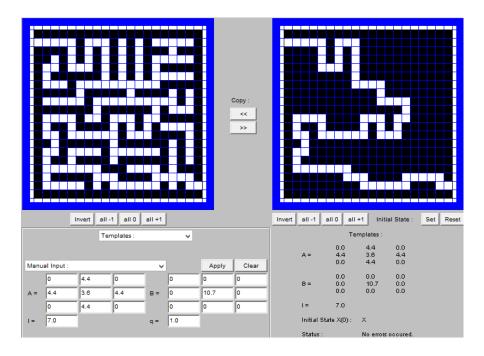

#### 1.6.5 Detector de conectividad global

Este ejemplo puede ser visto como un sistema que encuentra la salida en un laberinto; para este ejemplo se toman en consideración los siguientes puntos: La salida del laberinto tendrá un ancho de un pixel además de que éste tendrá que ser blanco, si el pixel es negro su salida tendrá que ser de color negro, si la entrada es un pixel blanco y tres de sus vecinos son de color negro su salida tendrá que ser de color negro de otra forma será de color blanco. En la siguiente figura se muestra los puntos anteriormente dichos.

Fig. 1.13. Pixeles a considerar para el detector de conectividad global, en estos casos el pixel central será el procesado.

Para mostrar esto se utilizarán las siguientes plantillas y valor de umbral.

$$A = \begin{bmatrix} 0 & 4.4 & 0 \\ 4.4 & 3.6 & 4.4 \\ 0 & 4.4 & 0 \end{bmatrix}, B = \begin{bmatrix} 0 & 0 & 0 \\ 0 & 10.7 & 0 \\ 0 & 0 & 0 \end{bmatrix}, I = 7.0$$

Con lo cual obtenemos la siguiente respuesta:

Fig. 1.14. Ejemplo de Detector de conectividad global

#### 1.7 Conclusiones

En este capítulo se han introducido los conceptos básicos de la CNN, estos conceptos incluyen el funcionamiento de la CNN y la arquitectura de una CNN. También se describió la unidad básica de las CNN llamadas neuronas o celdas, además se mostraron las ecuaciones que describen el funcionamiento de una neurona, se realizó una mención especial en las

plantillas debido a que éstas son muy importantes dentro de las CNN ya que indican a ésta qué tipo de procesamiento realizarán, ya sea para el procesamiento de imágenes o para realizar otro tipo de procesamientos que pueda realizar la CNN, como el resolver ecuaciones diferenciales. También fueron descritos los métodos para realizar la búsqueda de las plantillas.

Todos los conceptos anteriormente mencionados son importantes ya que con base a ellos se realizará tanto un simulador como una implementación física en un FPGA de una CNN.

Dentro de este capítulo se demostró el uso de la CNN como procesador de imágenes utilizando diferentes tipos de plantillas, algunos de estos procesamientos fueron el removedor de ruido, extractor de bordes, extractor de sombras y detector de conectividad global.

#### 1.8 Referencias

- [1] Leon O. Chua and L. Yang, "Cellular Neural Networks: Theory & Applications", IEEE Trans. Circuits and Systems, vol. CA-35, 1988, pp. 1257-1290.

- [2] Leon O. Chua and Tamás Roska, "Cellular neural networks and visual computing: Foundations and applications", Cambridge U.K., Cambridge University Press 2004, Ch. 2, pp. 7-34.

- [3] Valerio Cimagalli and Marco Balsi, "Cellular Neural Networks: A Review", E. Caianiello (ed): "Neural Nets WIRN Vietri-93", World Scientific, Singapore, 1944, pp. 55-84.

- [4] H. Harrer, "Multiple Layer Discrete-Time Cellular Neural Networks Using Time-Variant templates", IEEE Trans. On Circuits and Systems II vol. 40, no 3, March 1993, pp. 191-199.

- [5] Jesus Ezequiel Molinar Solís, "Circuito Integrado Analógico CMOS con Arquitectura de Red Neuronal Celular", M.C. I.E. CINVESTAV, México, D.F. 2002.

- [6] S. Parmaksizoğlu and M. Alçı, "A Novel Cloning Template Designing Method by Using an Artificial Bee Colony Algorithm for Edge Detection of CNN Based Imaging Sensor", Sensors, vol. 11, no. 12, pp. 5337-5359, May 2011.

- [7] Leon O. Chua and P. Thiran, "An Analytic Method for Designing Simple Cellular Neural Networks", IEEE Trans. On Circuits and Systems, vol. 38, no 11, November 1991, pp. 1332-1341.

- [8] I. Fijfar and F. Bratkovic, "Design of Monotonic Binary-Valued Cellular Neural Networks", CNNA '96, Fourth IEEE International Workshop on Cellular Neural Networks and their Applications, Seville, 1996.

- [9] M. Hanggi and G.]S. Moschtz, "An exact and direct analytical method for the design of optimally robust CNN templates", IEEE Trans. On Circuits and Systems, vol. 46, no. 2, 1999, pp. 304-311.

- [10] Zarandy, A. "The Art of Template Design", International Journal of Circuit Theory and Applications, 27, pp. 5-23, 1999.

- [11] J. A. Nossek, "Design and Learning with Cellular Neural Networks", Proc. IEEE International Workshop on Cellular Neural Networks and their Applications, Rome, Dec. 1994, pp. 137-146.

- [12] C. Guzelis and S. Karamahut, "Recurrent Perceptron Learning Algorithm for Completely Stable Cellular Neural Networks", Proc. IEEE International Workshop on Cellular Neural Networks and their Applications. Rome, 1994, pp. 177-182.

- [13] B. Mirzai, Z. Cheng and G. S. Moschytz, "Learning Algorithms for Cellular Neural Networks", Proc. IEEE Int. Symp. Circuits Systems, Moterey CA. June 1998, vol. 3, pp. 159-162.

- [14] Zou, F.; Schwarz, S.; Nossek, J. A., "Cellular Neural Network Design Using a Learning Algorithm". In Proc, IEEE International Workshop on Cellular Neural Networks and Their Applications (CNNA '90), Budapest, Humgary, 16-19 December 1990, pp. 73-81.

- [15] Tetlaff, R., Wolf, D. A. "Learning Algorithm for the Dynamics of CNN with Nonlinear Templates Part I: Discrete-Time Case". In Proc. IEEE International Workshop on Cellular Neural Networks and Their Applications (CNNA '96), Seville, Spain, 24-26 June, 1996, pp. 461-466.

- [16] T. Kozek, T. Roska and Leon O. Chua, "Genetic Algorithm for CNN Template Learning", IEEE Trans. On Circuits and Systems I, vol. 40, pp. 392-402, June 1993.

- [17] Shuo Y. W. and Lin C. T. "Image Descreening by GA-CNN Based Texture Classifications", Trans. Circuits and Systems, 2004, vol. 51, pp. 2287-2299.

- [18] Koji Nakai and Akio Ushida, "Design Technique of Cellular Neural Network", Electronics and Communications in Japan, Part 3, vol. 78, No. 3, 1995.

### Capítulo 2. Multiplexado en tiempo de una CNN

#### 2.1 Introducción

Una forma de procesar una imagen es haciéndolo como en [1], donde cada pixel es mapeado dentro de una CNN, esto es que cada pixel será procesado por una neurona que conforma la CNN.

Dentro de un punto de vista de implementación en hardware y software, éste es un enfoque muy exhaustivo debido a la cantidad de neuronas que se requerían. Por ejemplo, para imágenes de  $10 \times 10$  pixeles se tendría un total de 100 pixeles, con lo cual con el enfoque antes mencionado deberíamos de tener una CNN de  $10 \times 10$  neuronas, donde cada neurona procesará un pixel que compone la imagen y tener así un total de 100 neuronas. Sin embargo, actualmente las imágenes pueden llegar a ser mucho mayores de  $512 \times 512$  pixeles, con lo cual tendríamos un total de 262,144 pixeles con lo cual deberíamos de tener una CNN de  $512 \times 512$  neuronas, con un total de 262,144 neuronas. Como vemos en este enfoque, la CNN requerirá la misma cantidad de neuronas, lo cual lo hace inviable debido al consumo de recursos que para ésta se requieren. Una alternativa a este enfoque es multiplexar la CNN en la imagen como se muestra en [2-4].

La principal ventaja de esta técnica de multiplexar la CNN, radica en el hecho de que no se requiere una CNN del mismo tamaño que la imagen a ser procesada, sino que basta una CNN de tamaño reducido para poder procesar imágenes de diversos tamaños. Sin embargo, esta metodología conlleva ciertos errores, los cuales veremos posteriormente, además de que hay que tener ciertas consideraciones en el multiplexado para poder procesar las imágenes de cualquier tamaño.

## 2.2 Pasos para multiplexar en tiempo una CNN

Para multiplexar la CNN, primero que nada se debe de tomar en cuenta el tamaño de la CNN con la cual se va a trabajar. Por ejemplo, una CNN con tamaño de 4 × 4 neuronas, una de 8 × 8 neuronas, etc., y así tener bloques de la imagen con la cual se va a trabajar del mismo tamaño que la CNN, después se procederá a procesar cada uno de estos bloques en algún orden lexicográfico.

#### 2.2.1 Obtención de bloques

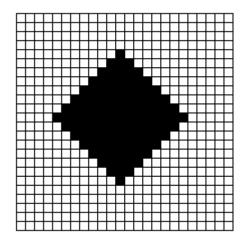

Para ejemplificar de una mejor manera la obtención de los bloques de la imagen, lo explicaremos con un ejemplo. De esta forma, tengamos en cuenta una CNN de  $8 \times 8$  neuronas y una imagen como la que se muestra en la Fig. 2.1, la cual es de  $24 \times 24$  pixeles (donde cada cuadrito representa un pixel). En este caso iremos tomando bloques de  $8 \times 8$  pixeles, con lo cual cada uno de estos bloques será procesado por el bloque de la CNN.

Fig. 2.1. Imagen de muestra.

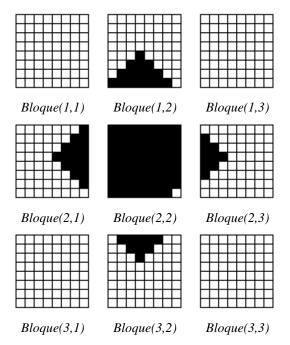

Por lo tanto, tendríamos una imagen conformada por 3 × 3 bloques con un total de 9 bloques, donde cada bloque está compuesto de 8 × 8 pixeles. Cada uno de los bloques, como mencionamos anteriormente, será procesado por la CNN de 8 × 8 neuronas. En la Fig. 2.2 se muestra cómo se dividiría esta imagen para formar dichos bloques.

Hay que considerar que no siempre la imagen será un múltiplo de la CNN que se tenga, es por esto que si la imagen no es múltiplo de la CNN se puede proceder a procesar la imagen de diferentes formas. Generalmente se puede aplicar alguna de las formas de las condiciones de frontera vistas en 1.2.5.

Fig. 2.2. Conformación de los bloques en una imagen dada.

#### 2.2.2 Orden lexicográfico

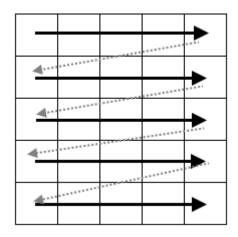

Los bloques escaneados por la CNN deben de seguir un orden lexicográfico, esto es un orden en el cual los bloques serán procesados, por ejemplo, en la Fig. 2.3 se muestra cómo se realiza un escaneo de izquierda a derecha y de arriba hacia abajo.

Fig. 2.3. Orden lexicográfico de Izquierda a derecha de arriba hacia abajo

Para ejemplificar este orden lexicográfico tomemos la imagen en bloques vista en la Fig. 2.2, donde se irán procesando los bloques en el siguiente orden: *Bloque*(1,1), *Bloque*(1,2), *Bloque*(1,3), *Bloque*(2,1),..., *Bloque*(3,3).

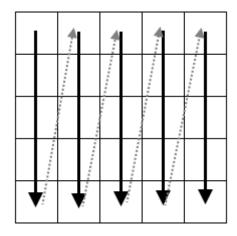

Otro ejemplo de orden lexicográfico sería como el mostrado en la Fig. 2.4, donde éste comienza a realiza el procesamiento de los bloques de arriba hacia debajo y de izquierda a derecha. Para ejemplificar este orden lexicográfico tomemos la imagen en bloques vista en la Fig. 2.2, donde se irán procesando los bloques en el siguiente orden: Bloque(1,1), Bloque(2,1), Bloque(3,1), Bloque(3,1), Bloque(3,2)..., Bloque(3,3). En nuestro trabajo hemos utilizado un orden lexicográfico como el mostrado en la Fig. 2.3.

Fig. 2.4. Orden lexicográfico de arriba hacia abajo de izquierda a derecha

#### 2.3 Errores en el multiplexado de la CNN

Otro punto a tomar en cuenta, es que en este enfoque de multiplexado de la CNN conlleva a dos tipos de errores en el cálculo de los pixeles en el borde para cualquier bloque de CNN, debido a que son calculados sin el efecto de sus pixeles vecinos.

Estos dos tipos de errores son mostrados en la ecuación (2.1) y la ecuación (2.2) respectivamente, las cuales corresponden a una CNN con vecindario de r = 1.

$$\varepsilon_{ij}^{A} = \sum_{i=1}^{i=3} a_{i,j+1} \, y_{i,j+1}(t) \tag{2.1}$$

$$\varepsilon_{ij}^{B} = \sum_{j=1}^{i=3} b_{i,j+1} \, sign(u_{i,j+1})$$

(2.2)

Donde la ecuación (2.1) representa el error debido a la ausencia de las salidas de las neuronas vecinas y la ecuación (2.2) representa el error debido a la ausencia de las entras de las neuronas vecinas y donde  $sign(\cdot)$  representa la función signo, esta función es representada en la ecuación (2.3).

$$sign(x) = \begin{cases} +1, & si \ x > 0 \\ 0, & si \ x = 0 \\ -1, & si \ x < 0 \end{cases}$$

(2.3)

#### 2.3.1 Reducción del error

Para reducir los errores en el procesamiento de los bloques vistos anteriormente, se realizan las siguientes consideraciones.

Para reducir el error de la ecuación (2.1) que es debida a la ausencia de las salidas  $y_{i,j}$ , se toma en cuenta lo siguiente.

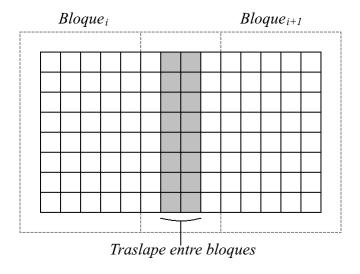

• Se hace un traslape entre dos bloques como es mostrado en la Fig. 2.5, el ancho mínimo de este traslape debe de ser dos veces el radio r del vecindario de la CNN. Se recomienda que este traslape sea mayor, sin embargo, para el procesamiento de una CNN donde importa más el resultado final que la evolución de las neuronas que conforman la CNN, con un vecindario con 2 veces r es suficiente.

Fig. 2.5. Traslape entre bloques de CNN.

En este punto hay que hacer la consideración de que debido al traslape de los bloques, existen pixeles que son procesados dos veces, sin embargo, el valor guardado y utilizado como resultado final depende del bloque. Por ejemplo, en la Fig. 2.5, los valores guardados para el primer bloque " $Bloque_i$ " se guardan los valores de salida y estado desde la primera hasta la penúltima columna que conforman el bloque; para el bloque " $Bloque_{i+1}$ " los valores guardados de salida y estado corresponde desde la segunda columna hasta la última. En otras palabras, la salida y estado del traslape (parte sombreada en la figura) corresponden para el lado izquierdo del bloque " $Bloque_i$ " y la parte derecha para el bloque " $Bloque_{i+1}$ ".

Otra consideración al traslape entre bloques, es que debido a esto, se incrementará la cantidad de bloques que hay dentro de la imagen.

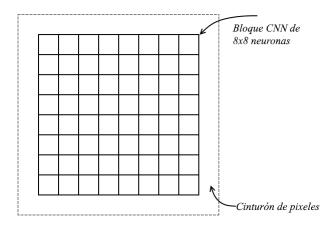

El error mostrado en la ecuación (2.2), es debido a la ausencia de las señales de entrada y la función "Saturación Lineal Simétrica" de los pixeles vecinos. Para minimizar este error se toma en cuenta la siguiente consideración:

Se coloca un cinturón de pixeles alrededor de la sub-imagen de la imagen original igual al radio de la CNN, por ejemplo si r = 1, se coloca un cinturón con ancho de un pixel, o si r = 2, se coloca un cinturón con ancho de 2 pixeles. Este punto se muestra en la Fig. 2.6 el cual muestra un cinturón con ancho de 1 pixel que corresponde a un vecindario con r = 1.

Fig. 2.6. Cinturón de pixeles en un bloque.

# 2.4 Repetición del tipo de bloques

Para un simulador, hay que tomar en cuenta que hay que ahorrar tiempo en el procesamiento de los datos de la CNN. Como vemos, al momento de multiplexar la CNN en la imagen, se pueden tener muchos casos donde los bloques puedan tener todos los pixeles en blanco o en negro. Tomando en cuenta lo anterior, basta con solo simular la primera vez que aparezca alguno de estos casos y guardar los valores obtenidos en la simulación. Después, cada vez que aparezca alguno de los casos anteriores, solo se necesitará rescatar los valores obtenidos en la primera simulación de estos.

Para ejemplificar esto tomemos el caso visto en la Fig. 2.2. En esta imagen observamos que tenemos 4 bloques que son totalmente blancos (sin considerar el traslape anteriormente mencionado) los cuales son Bloque(1,1), Bloque(1,3), Bloque(3,1) y Bloque(3,3), así solo sería necesario procesar un solo bloque blanco. En este caso basta con solo procesar el Bloque(1,1) y guardar sus resultados de salida y estado, para así cuando aparezcan el resto de los bloques blancos, en este caso el Bloque(1,3), Bloque(3,1) y Bloque(3,3), bastara con recuperar los datos guardados de estado y salida del Bloque(1,1) y colocarlo en el resto de los bloques. Con esta forma solo se procesarían un total de 6 bloques y no los 9 bloques obtenidos en la imagen, ahorrando de esta forma tiempo y cantidad de bloques procesados.

## 2.5 Algoritmo general para el multiplexado en tiempo de una CNN

Antes de realizar el multiplexado de una CNN para el procesado de una imagen, hay que crear la CNN. Esta CNN puede ser definida de diversas formas como es mostrado en [3] y [4], para poder así tener un mejor control sobre el algoritmo a implementar en el multiplexado. Además, hay que definir el tamaño de la CNN con la cual vamos a trabajar, y tenerlo en consideración para algunos de los pasos que conforman el algoritmo.

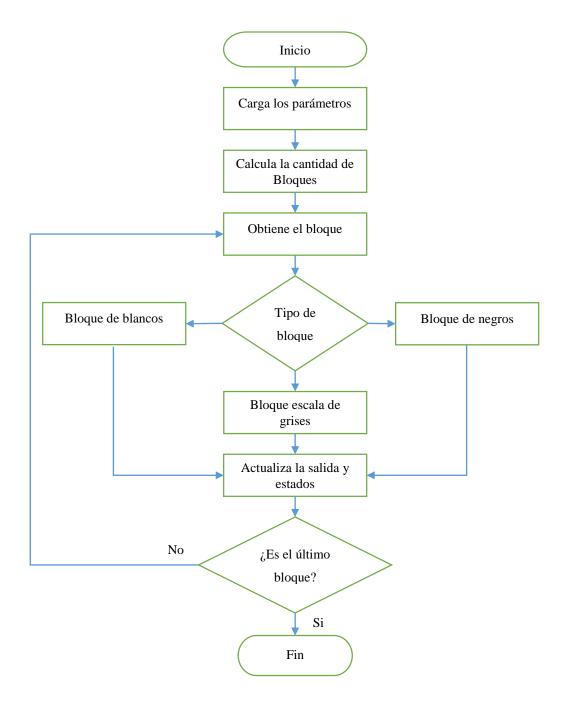

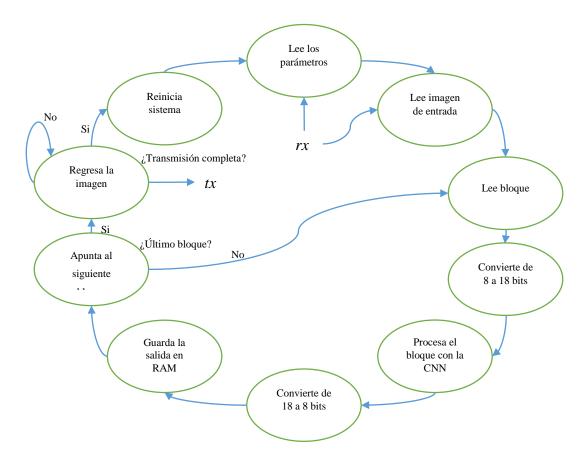

Un algoritmo general para el multiplexado de la CNN es mostrado en la Fig. 2.7. A continuación se explicarán cada uno de los bloques en forma breve.

Carga los parámetros: Este bloque se encarga de leer los diferentes parámetros que se pasarán a la CNN para realizar el multiplexado, como lo son los parámetros de plantillas y umbral, así como el valor de la frontera que se utilizará.

Fig. 2.7. Algoritmo general para el multiplexado en tiempo de una CNN.

Calcula la cantidad de bloques: Este bloque se encarga de calcular la cantidad de bloques que conforman la imagen, sin tomar en cuenta si hay bloques repetidos de blancos y negros, solo se realiza un cálculo general del total de bloques, esto basado en el tamaño de la CNN utilizada, además de tomar en cuenta el traslape y su tamaño.

**Obtiene el bloque:** Este bloque del algoritmo se encarga de llevar el control de los bloques que ya han sido procesados, además de indicar cuál será el próximo bloque a ser procesado, esto tomando en cuenta el orden lexicográfico utilizado en el procesamiento de la imagen.

**Tipo de bloque:** Este bloque del algoritmo se encarga de determinar el tipo de bloque de pixeles que ha obtenido el bloque del algoritmo "Obtiene el bloque", este indica si es un bloque blanco, negro, o uno de escala de grises (si se determina que es de escala de grises puede ser que también sea un bloque que tiene solo blancos y negros), y así lo envía a "Bloques de blancos", "Bloques de negros" o "Bloque escala de grises" dependiendo de cuál se determinó.

Bloque de blancos: Este bloque se encarga de realizar el procesamiento del primer bloque de pixeles que está totalmente en blanco. Después de esto, guarda los resultados obtenidos de la salida de la CNN y su estado, para poder ser utilizadas por los siguientes bloques totalmente en blancos y que no sean procesados de nuevo, de esta forma se ahorra tiempo en el procesado del multiplexado en tiempo de la CNN, ya que no se requiere realizar nuevamente los cálculos para estos bloques.

Bloque de negros: Este bloque se encarga de realizar el procesamiento del primer bloque de pixeles que está totalmente en negro, después de esto guarda los resultados obtenidos de la salida de la CNN y su estado, para poder ser utilizadas por los siguientes bloques totalmente en negros y que no sean procesados de nuevo, de esta forma se ahorra tiempo en el procesado del multiplexado en tiempo de la CNN, ya que no se requiere realizar nuevamente los cálculos en estos bloques.

**Bloque escala de grises:** Este bloque del algoritmo se encarga de realizar el procesamiento del bloque de pixeles que contiene tanto pixeles blancos como negros, o ya sea del procesamiento de un bloque que contenga pixeles en escala de grises.

Actualiza la salida y estados: Este bloque se encarga de guardar los resultados tanto de la salida como el estado de las neuronas, entregados por el procesamiento de la CNN. Esto lo realiza siguiendo lo mencionado anteriormente sobre el hecho de que dependiendo del tipo de bloque, qué resultados de las neuronas va a guardar, ya sea si guarda hasta la penúltima

columna o hasta la última o si guarda empezando desde la primera columna o desde la segunda columna de la CNN.

¿Es el último bloque?: Este bloque del algoritmo se encarga de determinar si el bloque procesado anteriormente es el último de los bloques o si no lo es, con esto determina si pasa a procesar el siguiente bloque o finalmente muestra los resultados con el bloque "Fin".

**Fin:** Este bloque se encarga de mostrar los resultados obtenidos en el procesamiento de la imagen utilizando esta técnica de multiplexado en tiempo de la CNN.

# 2.6 CNN para el multiplexado en tiempo

Una parte importante en el multiplexado de la CNN es realizar la CNN. Existen diversas formas de realizar esta CNN, como por ejemplo como se realiza en [1] y [5]. En las referencias [3] y [4] se dan dos ejemplos de cómo se pueden realizar estas CNN de diferente forma.

Como vemos en la referencia [3] se utiliza SIMULINK para crear la CNN y después multiplexarla, y en la referencia [4] se crea la CNN utilizando un lenguaje de programación. Para nuestro trabajo, utilizaremos SIMULINK, sin embargo, veremos más adelante que nuestra CNN creada en SIMULINK difiere a la creada en [3].

Esta CNN creada a través de un modelo por computadora debe de comportarse lo más parecido a una CNN diseñada con tecnología digital como lo es el FPGA, es por esto que deben de tomarse las consideraciones necesarias para poder realizar esto.

## 2.7 Conclusiones

En este capítulo se trató el tema del multiplexado de una CNN y su importancia de realizarlo, además de las desventajas y los errores que se generan al realizar esta técnica para el procesado de imágenes, sin embargo, se mostraron algunas formas de reducir estos errores creados.

También se mostró un algoritmo general para el multiplexado de la CNN, además de dar una pequeña explicación de cada uno de los pasos que conforman dicho algoritmo; este algoritmo es importante, ya que con base a este se realizará este trabajo de tesis. Como veremos más adelante, la CNN creada en este trabajo para el procesamiento de imágenes, utiliza gran parte del algoritmo mostrado en este capítulo.

## 2.8 Referencias

- [1] Leon O. Chua and L. Yang, "Cellular Neural Networks: Theory & Applications", IEEE Trans. Circuits and Systems, vol. CA-35, pp. 1257-1290, 1988.

- [2] Chi-Chien Lee and José Pineda de Gyves, "Time-Multiplexing CNN Simulator", IEEE Inter. Symp. On Circuits and Systems, 1994, vol. 6, pp. 407-410, 1994.

- [3] A. A. H. EL-Shafei and M.I. Sobhy, "A Time-Multiplexing simulator for Cellular Neural Network (CNN) using SIMULINK", IEEE Inter. Symp. On Circuits and Systems, 1998, vol. 3, pp. 167-170.

- [4] A. A. H. EL-Shafei and M.I. Sobhy, "A Time-Multiplexing simulator for Cellular Neural Network (CNN)", Cellular Neural Networks and Their Applications Proceedings, 1998 Fifth IEEE International Workshop on, pp. 14-18, 1998.

- [5] Leon O. Chua and Tamás Roska, "Cellular neural networks and visual computing: Foundations and applications", Cambridge U. K., Cambridge University Press, 2004, ch. 2, pp. 7-34.

# Capítulo 3. Descripción de una CNN multiplexada en tiempo con MATLAB y SIMULINK

## 3.1 Introducción

Como mencionamos en el capítulo anterior, realizar una CNN como la mencionada en [1] tomaría demasiados recursos tanto en software como en hardware, es por eso que se han propuestos trabajos como los mostrados en [2-4], donde se ha multiplexado la CNN dando buenos resultados. Estos trabajos se han enfocado principalmente en el procesamiento de imágenes.

El multiplexado de la CNN para imágenes representa una buena opción para su realización tanto en software y hardware debido a la disminución de cantidad de neuronas que se requieren para realizar el procesamiento de imágenes y con esto la reducción de recursos que se requieren para realizarla, ya sea en software o hardware, es por ello que en este trabajo realizaremos una CNN para el procesamiento de imágenes, esta CNN será de  $4 \times 4$  neuronas con vecindario de r=1.

En este capítulo, nos concentraremos en realizar un simulador de la CNN para posteriormente realizarla en hardware utilizando un FPGA y describiéndola en VHDL. Para realizar el simulador utilizaremos SIMULINK y MATLAB. Sin embargo, para realizar este simulador y poderlo hacer que coincida lo más posible a la que se realizará en VHDL se tomarán criterios en los cálculos, debido a que en VHDL la descripción del circuito lo haremos digital por lo tanto solo podremos utilizar cierta resolución numérica para estos.

La importancia de tener un simulador para nuestra CNN que realizaremos en hardware radica en el hecho de que necesitamos saber cómo se comportará nuestra CNN a la resolución de problemas, este simulador será utilizado para el procesamiento de imágenes.

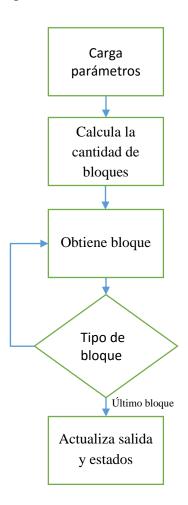

## 3.2 Algoritmo de una CNN multiplexada en tiempo

El algoritmo utilizado para crear el simulador con MATLAB y SIMULINK fue basado en el mostrado en la Fig. 2.7, sin embargo, este algoritmo lo adecuaremos para poder ser implementado utilizando tanto MATLAB como SIMULINK.

Este algoritmo es mostrado en la siguiente figura. Como vemos, parece diferir de aquel mostrado en la Fig. 2.7, sin embargo, como mencionamos anteriormente, este algoritmo toma en cuenta la parte del lenguaje en el que lo vamos a implementar. Además de esto, en el algoritmo se toma en cuenta que la creación de la CNN fue a través de SIMULINK.

Fig. 3.1. Algoritmo utilizado para el multiplexado de la CNN en tiempo.

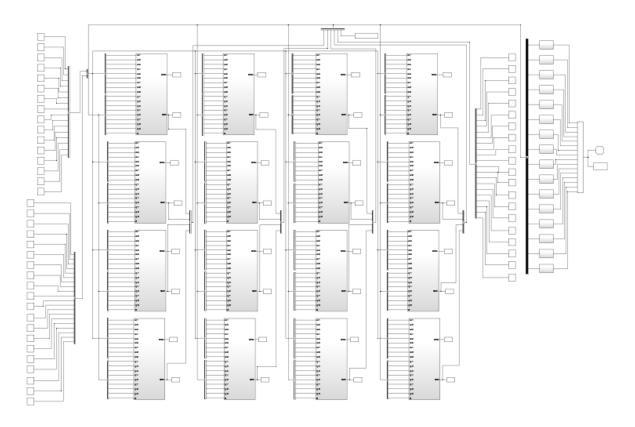

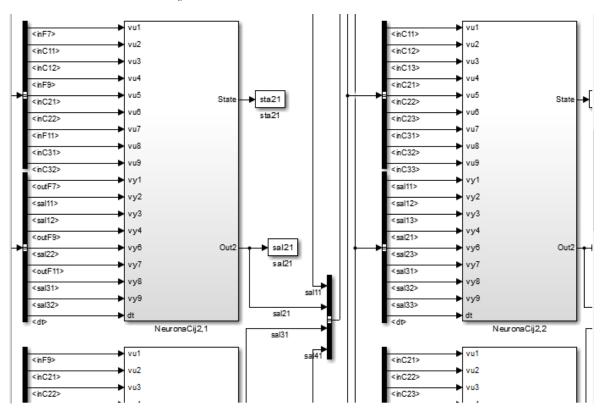

## 3.3 Creación de una CNN de 4 × 4 Neuronas en SIMULINK

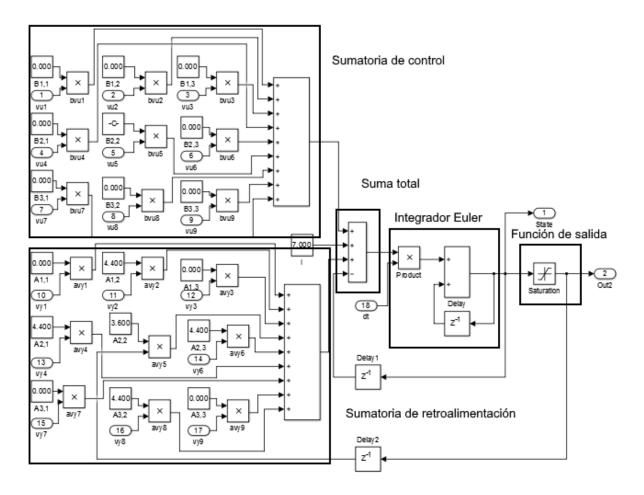

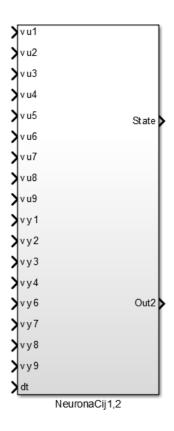

El simulador creado en este capítulo fue derivado de la ecuación de estado normalizada de la CNN, ecuación (1.3) vista en el primer capítulo, y para poder realizarlo se utilizó MATLAB y SIMULINK. El uso de SIMULINK es debido a que dicha ecuación de estado puede ser descrita en forma de bloques, además de que podemos crear la neurona y replicarla para crear la matriz de 4 × 4 neuronas y éstas procesen su información en forma paralela, de forma similar a como lo haría una CNN real.

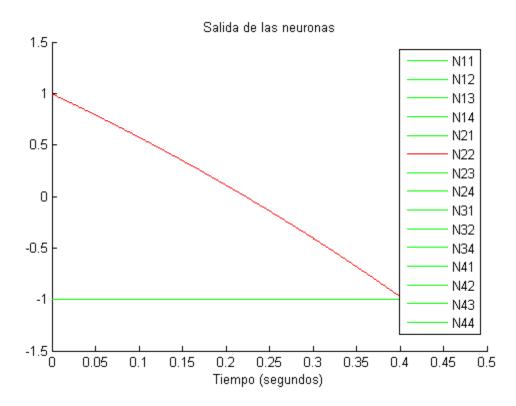

Antes de crear la CNN de 4 × 4 neuronas y de explicar el algoritmo general para el multiplexado de CNN, explicaremos cómo se creó la neurona para después reproducirla y crear la CNN; dicha neurona puede ser descrita en forma de bloques como se muestra en la siguiente figura.

Fig. 3.2. Diagrama a bloques de una neurona C (i, j).

Donde **Y** representa la matriz de las salidas de las neuronas dentro del vecindario, **U** representa la matriz de las entradas de las neuronas dentro del vecindario, **A** representa la matriz de retroalimentación, **B** representa la matriz de control, I representa el umbral, el símbolo  $\Sigma$  representa la sumatoria de los valores de las sumatorias de las plantillas y el valor negativo del estado  $x_{i,j}$ ,  $f(\cdot)$  representa la función de transferencia y finalmente  $y_{i,j}$  representa la salida de la neurona C(i,j).

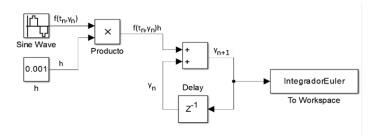

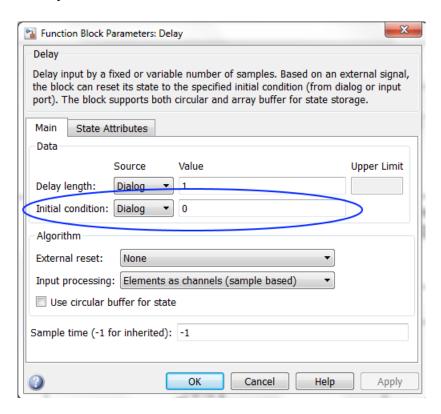

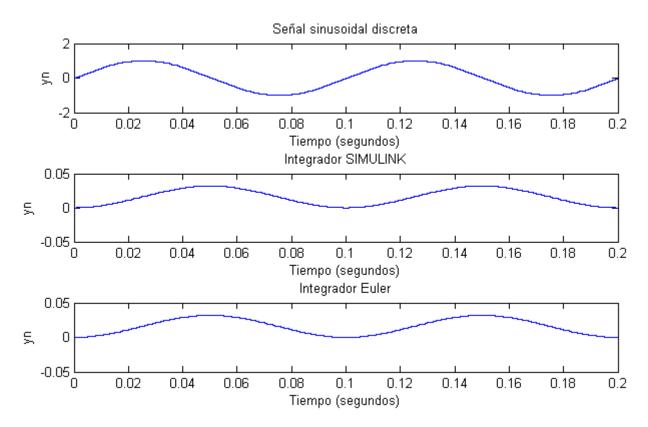

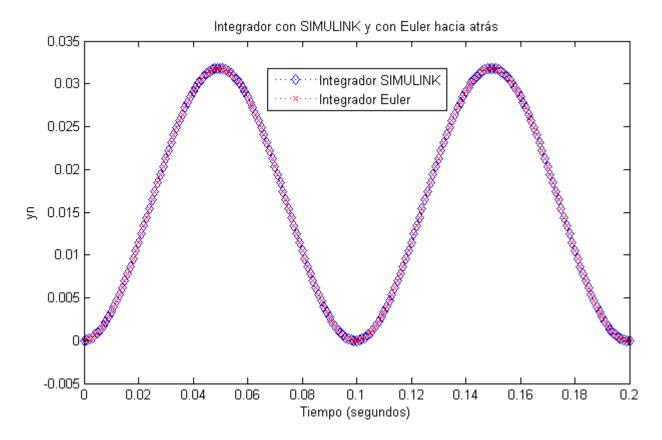

## 3.3.1 Integrador Euler

Para poder resolver la ecuación de estado de la CNN, se requiere resolver la ecuación diferencial y para poder realizar esto se requiere de hacer una integración numérica, como se observa en el diagrama a bloques, lo que quiere decir que cada neurona tendrá un integrador. Además debemos tener en cuenta que las neuronas trabajan en forma paralela lo que quiere decir que todas van resolviendo su respectiva ecuación diferencial al mismo tiempo que las demás. Es por esto que utilizaremos SIMULINK ya que permite describir la neurona y reproducirla para que resuelvan sus respectivas ecuaciones de estado en forma paralela.

Aunque SIMULINK incluye bloques para realizar integración numérica, se optó por crear otro bloque debido a que se implementará en hardware posteriormente, y así tener una simulación funcional con la cual se pueda verificar la implementación.

Aunque existen diversos métodos de integración numérica como Euler, Euler hacia atrás, Euler mejorado, y los métodos de Runge-Kuta, se optó por realizar el método de Euler hacia atrás debido a su sencillez y facilidad de realizarlo en hardware. En la siguiente tabla se muestran las diferentes fórmulas de los métodos de integración numérica.

Tabla 3.1. Fórmulas de integración numérica.

| Método            | Formula                                                                                                                                                                                                     |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Euler             | $y_{n+1} = y_n + f(t_n, y_n)h$                                                                                                                                                                              |

| Euler hacia atrás | $y_{n+1} = y_n + f(t_{n+1}, y_{n+1})h$                                                                                                                                                                      |

| Euler mejorado    | $y_{n+1} = y_n + \frac{f_n + f(t_n + h, y_n + hf_n)}{2}h$                                                                                                                                                   |

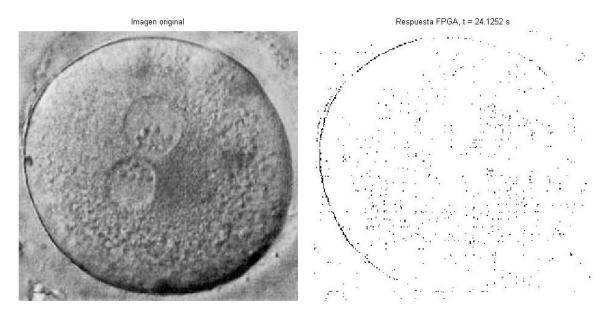

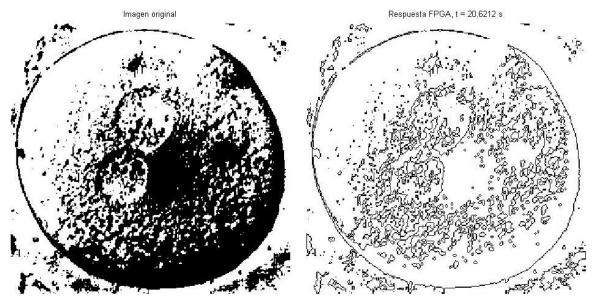

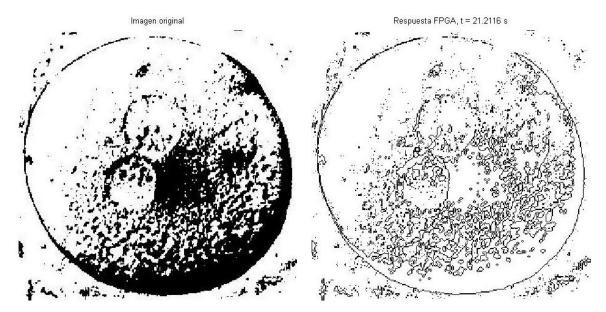

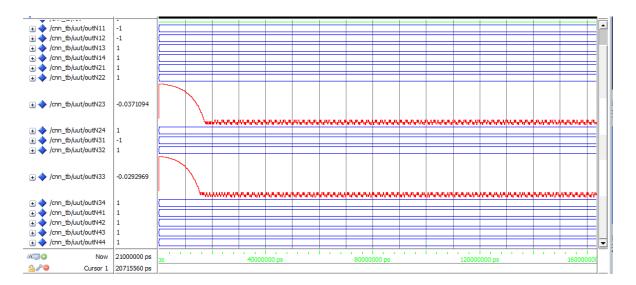

| Runge-Kuta        | $y_{n+1} = y_n + h\left(\frac{k_{n1} + 2k_{n2} + 2k_{n3} + k_{n4}}{6}\right)$                                                                                                                               |